基于嵌入式Linux和FPGA的千兆网数据传输的实现

|

- UID

- 871057

- 性别

- 男

|

基于嵌入式Linux和FPGA的千兆网数据传输的实现

引言

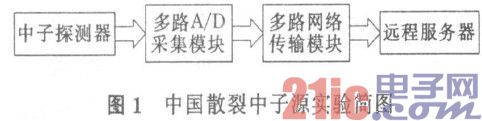

中国散裂中子源实验的简图如图1所示,其原理是把中子束打在被测样品(例如新药品或机翼材料)上,探测被反射的中子位置就能计算出样品的内部结构图像,其特点如下: A/D采集通道多,每个通道的数据带宽高,且需要把现场采集的数据传到远程服务器上。因此,要求数据传输模块既要成本低、微型化、具备网络功能,也要数据带宽高。

图1 中国散裂中子源实验简图

单片机或ARM具有微型化、低成本的特点,但数据带宽和灵活性不满足本项目;工控计算机数据处理能力强,有网络接口,但是体积过大,成本高;传统高能物理实验采用的VME系统也因体积大、数据带宽有限而不适合用在中国散裂中子源实验上。

FPGA有很高的性能,而且内部还集成PowerPC处理器、千兆网MAC等硬核资源,这使得在一块FPGA上就能构建一个完整的片上系统,使整个系统体积可以做的很小。在FPGA片内PowerPC硬核上移植嵌入式linux操作系统,用软件来实现网络传输协议可以解决用FPGA硬件描述语言实现TCP/IP协议难度大的问题。FPGA的高性能、高可靠性和Linux的灵活性完美结合在一个片内,能较好地满足本项目的需求。

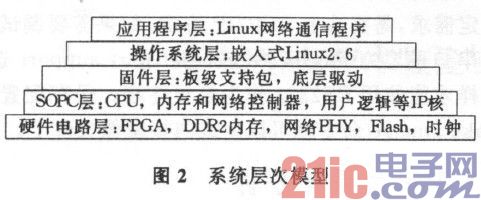

1 系统的总体构成及层次

本系统可以分为5个层次,如图2所示,

最低层为外围电路硬件层,每一层都是建立在其下一层之上。

2 系统外围电路的简介

本文在硬件上采用了实验室自行设计的电路板,用的是带PowerPC的xilinx Virtex4 FPGA,电路如图3所示。

图3 系统的硬件模块框图

3 SOPC的构建

SOPC (System on a Programmable Chip) 即可编程片上系统,把整个系统放到一块硅片上,是一种特殊的嵌入式系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

3.1 开发工具

Xilinx 公司提供了FPGA开发工具EDK(Embedded Development Kit),它带有大量可配置可定制的IP核,可以大大提高设计的效率,使设计者把主要精力放在设计系统架构上,能很方便的对FPGA进行模块化的重构和裁剪,提高设计的灵活性,减少了外围器件,符合SOPC的思想。

3.2 SOPC的总体构成

SOPC系统构建完成后的框图如图4所示,其中PowerPC405是已经固化在FPGA内部的硬核,工作频率设为300MHz,配置时要选择cache选项,否则运行嵌入式Linux会很慢。PowerPC405通过PLB(Process Local Bus)总线核和各个IP模块互联构建了一个完整的SOPC系统。

图4 FPGA内部各个IP模块框图

3.3 内存端口的设置

MPMC (Multi-Port Memory Controller)是DDR2内存控制器的IP核,它最多可以接八个数据端口,这样的好处是多个设备都可以通过各自的端口共享内存,本论文使用了四个端口:port0和port1都通过plb总线连接在PowerPC上,分别用于传输指令和数据,port2端口采用的是NPI(Native Port Interface)接口,用于接收A/D模块传输过来的用户数据,port3采用SDMA (Soft Direct Memory Access)接口,通过locallink总线和千兆网IP核相连。在对MPMC配置时要根据内存的型号、大小等实际参数来设置。

3.4 用户自定义数据接口IP核

开发工具虽然提供了一些常用的IP核,但是对于一些特定要求的逻辑,需要用户自己开发。由于从A/D采集板传送过来的数据速度很大,所以本论文在MPMC 的port2上采用NPI接口把A/D模块传过来的数据直接送入DDR2中。需要用硬件描述语言编写基于NPI接口的逻辑,并且还要编写基于PLB总线的IP核来实现对数据传输的控制,例如数据传输开始与停止、握手方式、数据包的大小等等。

3.5 千兆三态以太网硬核的配置

三态以太网TEMAC (Tri-Mode Ethernet Media Access Controller)是嵌在FPGA内部的硬核。本论文通过LocalLink总线使其连在内存控制器MPMC上,采用SDMA方式,使得数据直接从内存到网络接口而不必经过PowerPC的搬运, 这样在很大程度上减轻了CPU的负担,提高了数据传输速度。

4 板级支持包的生成

4.1板级支持包工具的选择和设置

先在http://git.xilinx.com/网站上下载device-tree.git,它是板级支持包(BSP)生成工具。解压后放在EDK安装目录下的EDKswlibbsp,之后点击Software-->

Software Platform Settings就可以发现并选择它了,如图5所示。

图5 板级支持包工具的选择

在device-tree下要把 bootargs的设置成console=ttyUL0,而不是默认的console =ttyS0,否则超级终端将没有输出。这是因为我们在调试时需要RS232串口作为超级终端,用的是XPS UART Lite核,但板级支持包默认的却是UART16500核。

4.2 dts(device tree)文件的生成

xilinx.dts文件是板级支持包工具device tree生成的,它记录了硬件信息。正是这个文件的存在操作系统才能知道本系统有哪些硬件及其属性。在EDK菜单中选择Software-->generate Libraries and BSP就会生成xilinx.dts文件。

5嵌入式Linux的移植

5.1安装用于PowerPC的交叉编译链并设置环境变量

先下载并安装德国DENX公司提供的开发环境编译套件ELDK4.1,用source 命令设置路径和交叉编译环境变量,再用export ARCH=powerpc命令使其支持PowerPC架构。

5.2 准备Linux内核及根文件系统

这不是一般的Linux内核,而是专门针对Xilinx FPGA的linux-2.6-xlnx.git。可以到git.xilinx.com网站下载最新版本的Linux内核。在http://xilinx.wikidot.com/网上下载根文件系统镜像压缩文件ramdisk.image.gz,把ramdisk.image.gz拷贝到内核文件夹的arch/powerpc/boot文件夹中。

5.3准备 device tree文件

需要把把EDK工程中板级支持包工具生成的xilinx.dts复制到嵌入式Linux内核文件夹arch/powerpc/boot/dts中,这样linux才能根据这个文件给硬件设备添加相应的驱动。

5.4内核的裁剪与定制

用命令make 40x/ virtex4_defconfig载入ML405开发板的内核配置,再用make menuconfig打开内核定制图形界面进行裁剪和定制,使满足自己的特定需求,需要选上TCP/IP协议。如果需要调试就要把串口驱动 xilinx uartlite serial port support选上。这样才能使用RS2323作为超级终端。保存配置后用make zImage命令就可以生成内核镜像文件了。

6 测试结果与分析

在EDK中选把硬件文件烧录到FPGA中, 把Linux镜像文件下载到内存中运行,这样一个系统就能运行起来了。编写一个基于socket的网络通信程序,把FPGA作为客户端,把PC机作为服务器端,从FPGA不断的向PC发送基于TCP协议的数据包,来测试每次发送的数据包大小和传输速度之间的关系。当发送的数据包大小为30000Byte时,用tcp/ip协议传输的速率是70Mb/s,用udp协议传输的速率是135Mb/s。

在一定范围内,每次发送的数据包越大,则网络传输速率就越大。传输的速度即与powerpc、内存、内部总线的频率及位宽有关系,也与操作系统及应用程序有关系。

7结束语

本文详细的介绍了基于Linux和FPGA的嵌入式千兆网数据传输的实现方法,测试结果表明传输速度能满足设计指标。由于FPGA和linux都具有很大的灵活性,会给将来系统的升级和变更带来很大方便。 |

|

|

|

|

|

|

- UID

- 931559

|

|

|

|

|

|