连接器电子电路设计图集锦TOP12 —电路图天天读(8)

|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

连接器电子电路设计图集锦TOP12 —电路图天天读(8)

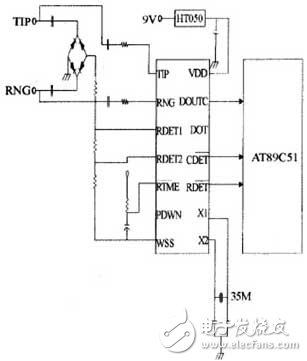

TOP8 电话网络报警系统连接器电路

系统主要由接收报警信息预处理电路与PC机组成(如图 1)。报警信息接收预处理电路通过接收电话网络传来的报警信息,并将报警信息格式化,再通过USB接口将信息传送给PC机。PC机接收传送回来的格式化信息,进行信息分析和差错处理,确认格式正确后再与数据库(ADO)中的用户数据进行比对,将报警用户的信息通过报警对话框弹出显示。

图3 HT9032的电路连接图

电话线上的直流和交流电压都高于报警主机的电压,需要在接口处加光耦,将程控交换机和报警器的电源隔离。要避免户外断线或户外非法并机,并且报警器没有摘机的情况下才报警。出现异常,光耦导通,集电极输出低电平给单片机,进行异常报警中断处理。用PNP的三极管控制继电器常开端的吸合和打开。当单片机发出摘机信号时,给三极管的基极低电平,三极管导通,继电器闭合,电话线两端的电阻降至300 nΩ左右,从而实现模拟摘机。当单片机发出挂机信号时,给三极管的基极高电平,三极管截止,继电器常开端打开,电阻上升至无穷,从而实现模拟挂机。

音频编码连接器应用电路设计攻略

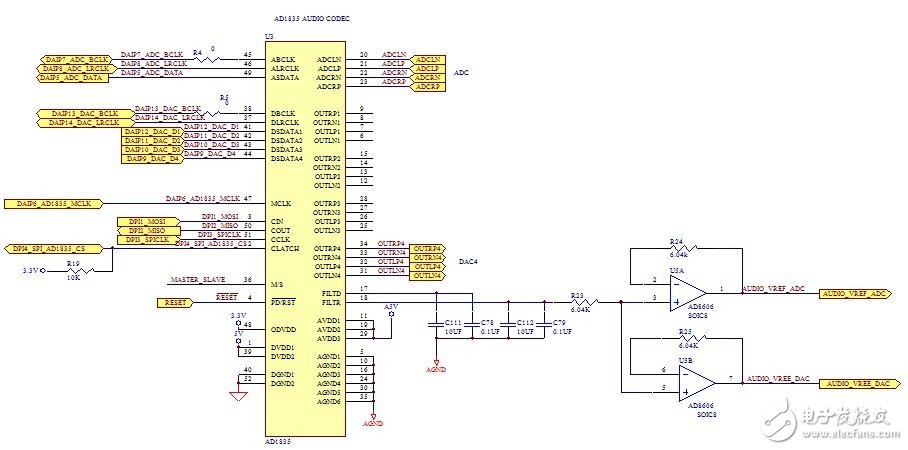

DSP处理器和AD1835A芯片的连接电路

DSP处理器通过DAI接口和AD1835A芯片相连。音频芯片的内部配置寄存器是通过处理器的SPI口来完成的。DPI4引脚被用来做为设备的片选,DAI引脚可以被配置成以时分复用(TDM)模式或者2线接口模式(TWI)从AD1835A传输串行数据。此外,我们只设计用到一路DAC4音频输出。如图1所示。

图1 AD1835A和DSP的连接电路图

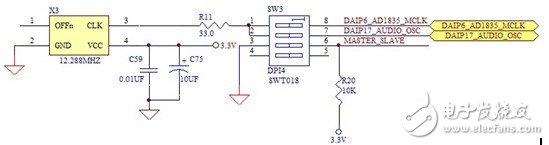

AD1835A时钟电路

AD1835A的主输入时钟(MCLK)可以由板上12.288Mhz的晶振产生,或者由DSP处理器上的DAI引脚提供,并通过开关SW3的1,2引脚位置配置。用DAI引脚产生晶振,允许多重器件同步,例如当数据来自索尼飞利浦数字接口(S/PDIF)接收器的时候,可以通过音频芯片输出。此时,S /PDIF的MCLK来自于AD1835A的MCLK。

开关的第三个位置决定了主从模式的选择。当开关的3和6相连时,即开关闭合的状态,MASTER_SLAVE为低,主模式,AD1835的串行接口来提供帧同步和时钟信号;3和6断开时,即开关关闭的状态,MASTER_SLAVE为高,从模式,DSP处理器需要提供帧同步和时钟信号,默认开关为闭合状态。

图2 AD1835A时钟电路图 |

|

|

|

|

|