|

- UID

- 1029342

- 性别

- 男

|

1 引言 随着网络和多媒体技术的发展,视觉通信的重要性和需求急剧增加,如桌面视频会议、移动终端、基于因特网的视频通信等。这些视觉信息内涵丰富,但数据量大,必须压缩数据。但采用多种方法压缩图像数据,其数据量仍然巨大,这就对计算机处理速度、传输介质、传输方法和存储介质提出较高要求。因此,数据压缩作为数据图像处理的关键技术之一,对研究图像压缩编码技术具有重要价值。

嵌入式微处理器中,DSP具有灵活、高速、便于嵌入式应用等优点,特别适合复杂算法处理的应用。数字视频图像压缩系统利用DSP作为其嵌入式平台,充分发挥其性能优势,较好地提高编码效率,满足图像实时处理需要。因此,这里介绍一种基于TMS320VC5509A型DSP的视频压缩系统。

2 静止图像的压缩编码标准JPEG

JPEG(Joint Photographic Experts Group)是由国际标准化组织(ISO)提出面向静止图像编码的标准,其处理方法依次使用离散余弦变换、量化、Z行扫描、游程编码和不变字长编码。JPEG算法定义了以下4种运行模式:

(1)基于DCT顺序型模式按照从左到右、从上到下的顺序对图像进行扫描和编码,称为基本系统。

(2)基于DCT递增模式 按照从粗到细的顺序对一幅图像进行编码,适用于传输时间长、用户喜欢图像从粗糙到清晰的场合。

(3)无失真编码模式保证重建图像与原始图像完全相同。

(4)分层编码 采用各种分辨率对图像进行编码。

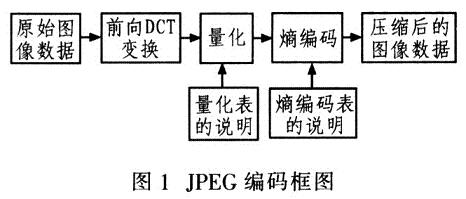

该系统采用基本系统模式。图1是JPEG的编码框图。

3 硬件系统设计

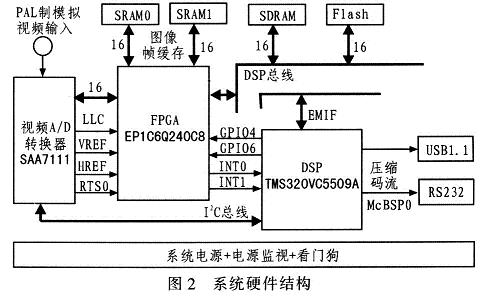

该视频压缩系统直接与PAL制摄像头的输出端相连,来采集、预处理和压缩现场图像,再以USB或RS232方式将处理后的图像数据传给上位机。图2为视频压缩系统硬件结构图。

该系统硬件设计以TI公司的TMS320VC5509A型数字信号处理器为核心,包括视频采集电路、FPGA预处理电路、存储器扩展、系统电源和看门狗电路等。系统中TMS320VC5509A为中央处理器;SDRAM为DSP外扩数据存储器;Flash为程序存储器,用于系统上电自举;模拟摄像头与视频 A/D转换器负责视频图像采集;FPGA用于地址译码、隔行运算,控制两片SRAM用于缓存视频A/D转换器转换后的数字图像。从系统设计成本考虑,这里选用Altera公司的可编程逻辑器件EPIC6Q240C8型FPGA。该器件是Cyclone系列器件中一款非BGA封装的可用I/O引脚最多的 FPGA。

3.1 视频采集电路

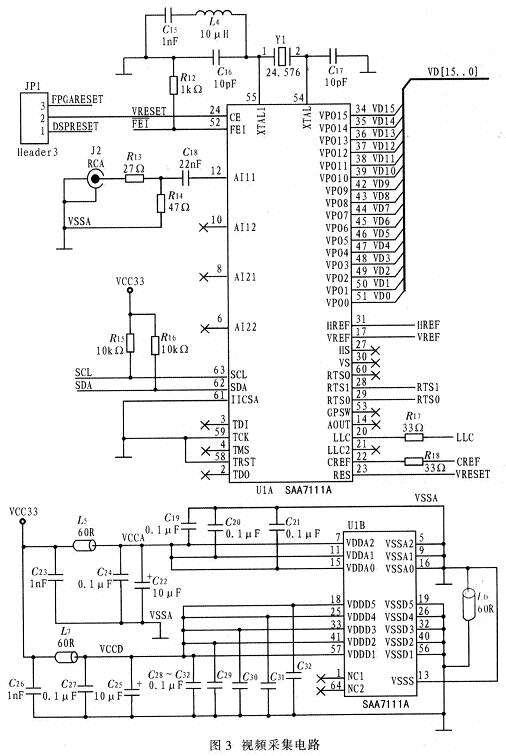

该系统选用的视频解码器为Philip公司的高性能视频A/D转换器SAA7111。该器件是一款广泛应用于桌面视频、多媒体、数字电视、图像处理、视频电话的高性能视频输入处理器件。该器件采用3.3 V的CMOS电路,高度集成模拟前端和数字视频编码器;包括2路模拟视频处理通道,1个时钟产生电路,1个自动箝位和自动增益控制电路,1个多制式数字解码器,1个亮度/对比度/饱和度控制电路,以及色彩空间矩阵。SAA7111输出为16位VPO总线,支持不同位宽的数据输出格式。SAA7111支持的输出格式包括:12位YUV411,16位YUV4:2:2,8位CCIR-656、16位565RGB以及24位的888RGB。图3为视频采集电路。

3.2 存储器选型

选择存储器应从以下方面考虑:首先图像压缩算法中间数据量大,要求处理器的片上内存尽可能大,尽量避免对外部存储器读写操作。VC5509A的片上存储器包括32 Kx16位DARAM,96 Kx16位SARAM,共128 K位的存储空间。其中DARAM为双地址,在每个周期内可以对其进行两次操作(2次读,两次写,一次读和一次写),这样大大增加片上存储器的利用率;其次,VC5509A片上资源丰富,包括I2C总线(多主从接口),3个McBSPs(1个与多媒体卡/数字加密卡MMC/SD串行接口复用引脚)。利用 FC总线对SAA7111的片内控制寄存器进行读写操作,非常方便实时控制SAA711 1的工作状态;利用McBSP配合DMA,软件编程实现UART功能,无需专门的硬件UART,从而节省电路板空间:VC5509A采用144引脚 LQFP封装,便于安装、调试;VC5509A功耗小,工作在200 MHz主频下,功耗仅100 mW,非常适合嵌入式应用。

3.3 DSP供电电源电路

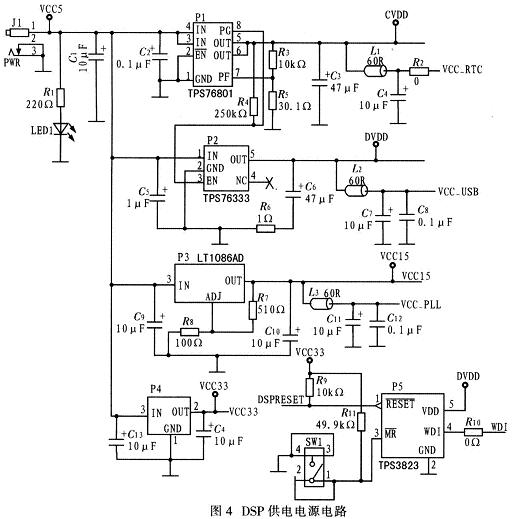

DSP基本系统由独立的电源系统供电,而硬件平台的其他器件共用另一套电源供电系统。为了降低系统功耗,DSP一般采用低电压供电.并且采用I/O和 CPU内核分开供电方式。VC5509A不同的工作频率要求不同的核电压,200 MHz为1.6 V,144 MHz为1.35 V,108 MHz为1.2 V。DSP的I/O电压为3.3 V。

DSP供电电源电路如图4所示。选用TI公司的两款LDO电源器件TPS76801和TPS75833分别为DSP提供内核电压和I/O电压。

TPS76801能给CPU内核提供最大1 A的电流,电压在1.2~3 V范围内可调。

调整TPS76801的输入电阻值得到1.6 V,1.35 V,1.2 V的核电压,DSP相应工作在200 MHz,144 MHz,108 MHz的频率下。而TPS75833能提供最高3 A的I/O电流,对于低功耗的TMS320VC5509A,这已足够保证其工作在最大负荷状态。 |

|