[导读] 本文选用TI公司的双核 DSP OMAP-L138作为本设计的微处理器,并实现了一种数字示波器微处理器硬件设计。

关键词:硬件设计数字示波器

随着通信技术的迅猛发展,电信号越来越复杂化和瞬态化,开发人员对测量领域必不可少的工具——数字示波器的性能提出了越来越高的要求。最大限度提高实时采样率和波形捕获能力成为了国内外众多数字示波器生产厂商研究的重点,实时采样率和波形捕获率的提高又必然带来大量高速波形数据的传输、保存和处理的问题。因此,作为数字示波器数据处理和系统控制的中枢,微处理器性能至关重要。本文选用TI公司的双核 DSP OMAP-L138作为本设计的微处理器,并实现了一种数字示波器微处理器硬件设计。

数字示波器的基本架构

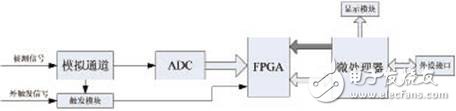

目前数字示波器多采用DSP、内嵌微处理器型FPGA或微处理器+FPGA架构。虽然内嵌微处理器型FPGA灵活性强,可以充分进行设计开发和验证,便于系统升级且FPGA外围电路简单。但是该类型FPGA属于高端FPGA,价高且供货渠道难得,不适合低成本的数字示波器使用。若单独使用 DSP,虽然其数据处理能力强大,运行速度较高,但DSP的控制能力不突出,且数字示波器的采样率越来越高,DSP内部不能做数据流降速和缓存,当设计采用高实时采样率的 ADC,就得选用频率更高且内部存储资源更丰富的DSP,而此类DSP一般都价格昂贵,同样不适合低成本的数字示波器使用。因此,微处理器+FPGA架构的方案是本设计首选。微处理器+FPGA架构的数字示波器的系统结构图如图1所示:

图1 微处理器+FPGA架构的数字示波器系统结构图

被测信号经模拟通道运放调理后送到ADC器件;ADC转换器将输入端的信号转换成相应的数字信号并经过FPGA缓存和预处理;微处理器对采样得到的数字信号进行相关处理与运算;最后将波形送到屏幕上显示,完成一次采集过程。同时采集过程中触发电路不断监测输入信号,看是否出现触发状态,触发条件决定了波形的起始位置,触发系统能够保证被测波形能够稳定的显示到屏幕上。

微处理器选型

本设计实时采样率高达2Gsps,需要微处理器实时处理的波形数据量很大。同时微处理器要实现模拟通道控制、高速ADC采样控制、波形数据存储控制、LCD显示控制等。因此兼具强大的数据处理能力和优异控制能力的微处理器成为本设计首选。

基于这些要求,本设计选择了TI公司的OMAP- L138 DSP。此芯片是TI公司2009年推出的一款高性能处理器芯片。该芯片特点如下:

1、采用C6748 DSP内核与ARM9内核的双核结构,可实现高达300 MHz的单位内核频率。利用片上ARM9,开发人员可充分利用DSP内核支持高强度的实时处理计算,同时让ARM负责非实时任务。

2、丰富的内部存储器资源。其中ARM核内部有16KB的L1程序Cache和16KB的数据Cache;DSP核采用二级缓存结构,包括 32KB 的L1程序Cache、32KB 的数据Cache和256KB 的L2统一映射SRAM,该二级高速缓存结构可以为所有载入、存储以及处理请求提供服务,可以为CPU提供高效、高速的数据共享;此外在ARM核与DSP 核之间还有高达128KB的片上RAM,可被ARM核、DSP核以及片外存储器访问。

3、丰富的外设资源。主要包括1个EMIFA口,可接16bit SDRAM或者NOR/NAND Flash;1个EMIFB口,可接16bit的DDR2(最高频率150MHz)或16bit mDDR (最高频率133MHz);3个UART接口;2个SPI接口;2个I2C接口;1个EMAC控制器;1个USB2.0接口和1个USB1.1接口;1个 LCD控制器;1个SATA控制器;1个uPP接口;1个VPIF接口;4个64位通用定时器。丰富的外设资源不仅可以为示波器提供与PC机、便携式 USB接口设备通信的接口,而且极大减少DSP外围电路的设计规模,

4、低功耗。采用1.2V内核电压,1.8V或3.3V I/O接口电压,在深度睡眠模式下功耗仅有6mW,正常工作模式下功耗约为420mW。

此外OMAP-L138为浮、定点兼容DSP,使用硬件来完成浮点运算,可以在单周期内完成,这一优点在实现高精度复杂算法时尤为突出,为复杂算法的实时处理提供了保证。OMAP-L138还可与C6748 DSP实现引脚对引脚兼容,从而使客户可采用不同的处理器同时开发多种不同特性的产品。

数字示波器系统硬件结构设计

本设计ADC选用Atmel公司的AT84AD001,该芯片有两个通道,每个通道采样率高达1Gsps,拼合可实现2Gsps的实时采样率;FPGA选用 Xilinx公司Spartan-3A系列的XC3S400A芯片,该芯片内有8064个逻辑单元,360Kbit块RAM,56Kbit分布式 RAM,4个数字时钟管理模块(DCM),311个I/O口。300KB容量的SRAM芯片外挂在FPGA上作深存储用,由于SRAM存储器容量比 FPGA内部缓存FIFO大得多,能够存储更多的波形数据,因而能观察到更多的波形细节。采用64Mbit容量的SPI Flash存储示波器掉电需要保存的数据,例如程序代码、Boot loader程序、中英文字库、开机画面等。

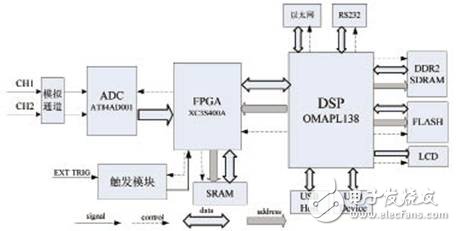

基于OMAP-L138的示波器硬件系统结构图如图2所示:

图2 数字示波器系统结构图

本设计中,被测信号进入模拟通道调理后送入ADC,ADC对模拟信号采样、量化后,进入FPGA数据流降速和数据同步处理,然后根据存储深度要求选择存入 FPGA内部FIFO或者存入片外SRAM,待FPGA内部FIFO或者片外SRAM满标志有效后,DSP读取采样数据存入DDR2 SDRAM,并完成一系列复杂的处理和运算,如FFT、插值和滤波等,再存入在DDR2内拓展的显示存储区,待需要显示时再由DSP读取显存中的数据通过内部集成的LCD控制器采用DMA方式将数据送到LCD显示,完成一次采集过程。

OMAP-L138与DDR2的接口电路设计

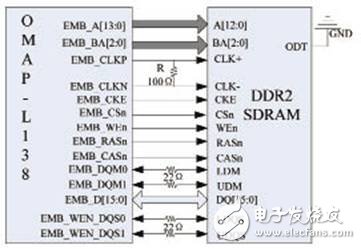

OMAP- L138内部集成的DDR2/Mobile DDR控制器可外接工作频率150MHz的DDR2 SDRAM或者工作频率133MHz的Mobile DDR。本设计采用DDR2 SDRAM作为系统后级波形数据缓存器。较之SDRAM,DDR2 SDRAM不仅读写速度可大幅提高,存储容量更是得到极大扩展,示波器因而能够存储更多波形数据并观察到更多的波形细节,提高示波器对复杂信号和瞬态信号的捕获概率。本设计的DDR2 SDRAM选用镁光公司的DDR2 800内存颗粒,型号为MT47H64M16,容量为1Gbit,核心工作电压为1.8V,核心工作频率为400MHz,由于OMAP-L138内部的 DDR2控制器最高工作频率为150MHz,所以此系统中DDR2需要降频使用。OMAP-L138与DDR2的接口连接示意图如图3所示:

图3 OMAP-L38与DDR2的接口连接示意图

DDR2 的信号线包括时钟、数据和命令三部分。本设计由DDR2控制器提供差分时钟CLK+和CLK-给DDR2,,差分时钟之间并接一个100Ω的匹配电阻,用以消除时钟的毛刺并限制驱动电流;数据部分主要完成数据传输工作,包括数据线DQ[15:0]、数据同步信号DQS(本设计LDQS对应数据线低八位,UDQS对应数据线高八位)、数据信号屏蔽线DM(在突发写传输时屏蔽不存储的数据,LDM对应数据位低八位DQ[7:0],UDM对应数据线高八位 DQ[15:8]),本设计在DQS信号和DM信号上串接一个22Ω的电阻,起抗干扰和滤波作用,提高信号质量;命令部分包括行地址选通信号RASn、列地址选通信号CASn、写使能信号WEn、片选信号CSn、时钟使能信号CKE以及芯片内部终端电阻使能ODT,主要完成寻址、组成各种控制命令以及内存初始化工作。本设计由于DDR2控制器内没有终端电阻,因此将DDR2 SDRAM的ODT信号直接接地使DDR2芯片内的终端电阻无效。

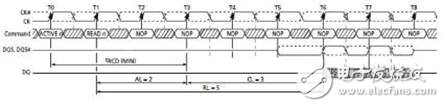

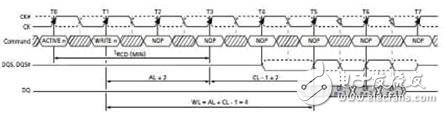

DDR2的读、写时序图分别见图4和图5:

图4 DDR2的读数据时序图

图5 DDR2的写数据时序图

以太网的接口电路设计

用示波器测量电信号时,信息和测量结果便捷的保存和共享变得日益重要。若数字示波器提供以太网接口,开发人员就可以方便地将测量数据和结果通过网络共享,实现远程调试;也可以将波形数据通过网络上传到PC机上,在PC机上实现波形数据的处理、分析和显示。

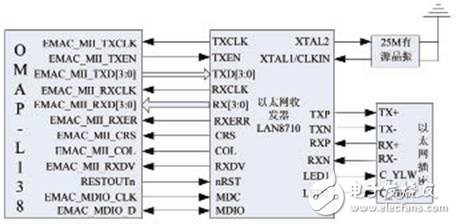

OMAP-L138内部集成的以太网控制器(EMAC)支持IEEE802.3标准,支持10Base-T和100Base-T两种以太网标准,有全双工和半双工两种工作模式可供选择,提供了MII和RMII两种以太网接口。

选用LAN8710以太网收发器,该以太网收发器提供MII和RMII两种以太网接口。本设计采用MII接口实现LAN8710与EMAC的互联。MII接口包括一个数据接口,一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道有4根数据线、时钟和控制信号,其中管理接口是双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。管理接口的时钟MDC由EMAC提供,最高可达 8.3MHz;数据信号MDIO是双向接口,与MDC同步,控制收发器并从收发器收集状态信息。可收集的信息包括链接状态、传输速度与选择、断电、低功率休眠状态、TX/RX模式选择、自动协商控制、环回模式控制等。

以太网接口连接示意图如图6所示:

图6 以太网接口连接示意图

结论

本设计有以下优点:数据处理与系统控制同步执行;微处理器内部存储资源丰富,且采用二级缓存结构,系统响应速度快;外设资源丰富,提供了如 USB接口、RS232接口和以太网接口等与PC机互联的接口,方便示波器上采集到的波形数据在PC机上实时处理和在线调试;外部存储器资源丰富,采用 1Gbit 容量的DDR2 SDRAM作后级波形数据缓存区和显示数据缓存区,能够存储更多波形数据,观察到更多波形细节。由此可见,采用该示波器系统可大幅提高数字示波器的数据处理能力和波形捕获率,整机的响应速度也将上一个台阶。

|