ARM Cortex-M23是采用TrustZone技术的处理器中尺寸最小、能效最高的处理器。对系统安全的小型嵌入式应用来说,使用基于ARMv8-M baseline 的Cortex-M23处理器则是最佳解决方案。

本文中,我将带各位领略全新Cortex-M23处理器的全新特性:

Cortex-M23最重要的特色是加入了TrustZone安全基础技术

极紧凑的架构与流水线

强化的调试纠错(Debug)和追溯能力(Trace)(能显著提高开发者的效率)

改进的存储保护单元MPU(该单元定义软件的访问权限;全新设计提升程序访问的效率;改进了的存储区域Region的配置方法)

新增多条增强性能的指令

1. 为ARMv8-M量身打造的TrustZone技术:系统安全的基础

TrustZone技术为ARMv8-M量体裁衣,在每一台搭载Cortex-M23处理器的设备上以硬件形式实现可信代码(Secure Code)和非可信代码(Non-Secure Code)的强制隔离。借助TrustZone,开发人员仅需单个处理器就可以实现安全类嵌入式应用设计,而此前则必须借助多个处理器才可建立可信区域和非可信区域之间的物理隔离。使用Cortex-M23处理器设计的系统可以出色的满足多项安全需求,如设备识别管理、高价值固件保护、软件认证、安全根等等。

采用TrustZone技术的Cortex-M23处理器具备以下两种安全状态:

安全状态(Secure State) – 可以访问安全和非安全资源(存储、周边设备等)

非安全状态 (Non-Secure State)– 仅可访问非安全资源

两种安全状态下代码执行的状态切换和资源访问均由硬件监管——在保证系统确定性的前提下最大限度地降低了状态切换的管理成本——这也是所有Cortex-M处理器的标志性功能。

2. 紧凑的两级流水线处理器

Cortex-M23虽然是一款简单的两级流水线冯诺依曼处理器(Von Neumann processor),却足以支持全套ARMv8-M Baseline指令集。熟悉Cortex-M0+的用户一定可以迅速注意到Cortex-M23使能效最大化的众多相似特色:WFI(中断等待)/WFE(事件等待)睡眠/深度睡眠模式、退出中断时睡眠、SysTick定时器和可选的单周期Fast-IO等。

ARMv8-M Baseline指令集共包含80条左右的Thumb指令,其中大多数都是16位指令(为了尽可能提高代码密度),但仍有一些是为了提升效率而设置的32位指令。Cortex-M23支持所有的ARMv6-M指令,以帮助开发人员轻松地将代码从Cortex-M0和Cortex-M0+移植到Cortex-M23。此外ARMv8-M Baseline指令集中还加入了多条新指令以提升系统效率,例如条件执行、互斥访问、硬件除法运算以及可携带指令。

3. 强化的调试纠错(Debug)与追溯能力(Trace)

单纯依靠高效安全的32位处理器是无法在目标应用领域内实现成功的开发和部署的。事实上,软件开发的成本通常超过生产和硬件IP费用的总和。相对其他ARMv6-M处理器,Cortex-M23引入了更多可配置的硬件断点和数据视点,以帮助设计人员更轻松地完成软件的开发与调试。除了Cortex-M0+ 处理器中就已提供的微型跟踪缓冲器(MTB),Cortex-M23还提供了一个可选的嵌入式跟踪宏单元(ETM)。借助这些选配的功能模块,芯片设计师可以根据需求,在Trace的性价比和功能完整性之间进行选择。

4. 用于任务隔离的存储保护单元

Cortex-M23还包括可选的、基于全新PMSAv8架构的存储保护单元(MPU)。经过改进后的MPU使用起来也更加简单。安全和非安全状态都拥有自己独立的MPU,因此在任何一个状态下都可以最多"保护"多达16个区域。每个区域都由一个基地址、终止地址、访问权限和存储属性设置来描述。在多任务环境下,操作系统可以在任务上下文切换时重新配置MPU、定义每个任务的存储器访问权限。例如,配置MPU以允许应用程序访问全部或部分的数据、外设等等。通过保护限定之外的数据免遭污染,阻止未经授权的代码访问许可之外的外设,MPU可以显著提地升系统可靠性。

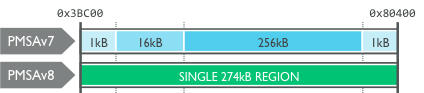

更易设置的存储区域

Cortex-M23的存储保护架构采用基地址和中止地址比较的方式来定义存储区域,而相对此前架构中基地址必须对齐到存储区域大小(而存储区域的大小必须是2的整数次幂)的限制,这项改进极大的简化了软件的复杂度。尤其是在通常情况下,存储区域尺寸不是完美的2的整数次幂,相对过去消耗多个Region来拼凑一个非对齐区域的做法,Cortex-M23的MPU能有效减少资源的浪费(如上图所示)。

5. 全新ARMv8-M Baseline指令

对比ARMv6-M,Cortex-M23加入了许多全新的指令,这丝毫没有减小Cortex-M系列处理器的超高能效。大多数新指令(除用于TrustZone安全扩展的之外)都继承自ARMv7-M的架构指令集,从而进一步拓展了Cortex-M23的性能,与Cortex-M0+ 处理器形成鲜明的对比。

5.1安全扩展

ARMv8-M采用的TrustZone安全技术为Baseline指令集补充了全新的安全指令,包括安全网关(SG)、非安全回调(BXNS、BLXNS)以及权限测试(TT)指令。更多详细内容,请参考Joseph Yiu编写的《ARMv8-M 架构介绍》。

5.2 暗代码

我们把无法读取代码内容而仅支持代码执行的代码,称为暗代码,这一概念借用于暗物质仅可推算其存在但无法感知的特性。借助从ARMv7-M继承的MOVW/MOVT指令,相对Cortex-M0/M0+,Cortex-M23对暗代码(Execute-Only)的支持也获得改善, 开发人员可以通过2条32位MOVW和MOVT指令的组合将一个32位的立即数“隐藏”到暗代码中——无需额外的数据读取过程。

5.3代码优化

从ARMv7-M继承的“条件比较跳转”指令(CBNZ/CBZ )可以提高很多“条件分支代码”的执行性能。支持大偏移量的立即跳转指令 (从ARMv7-M继承的)可以跳转到遥远的目标程序分支;硬件整数除法指令(从ARMv7-M继承的SDIV/UDIV)则可以减少除法运算的执行周期。

5.4 互斥操作

Cortex-M23从ARMv7-M继承了用于多核数据同步的专用指令,使得Cortex-M23有能力遵守多核系统中维护数据一致性的硬件规则——确保多个处理器以同样的机制处理同步信号。此外,为了对C11/C++11的原子操作提供更好的支持,Cortex-M23还新增ARMv8-A(Thumb 32版本)中最先引入的Load-Acquire与Store-Release指令,同时还包括了支持“互斥操作”指令变种。 |