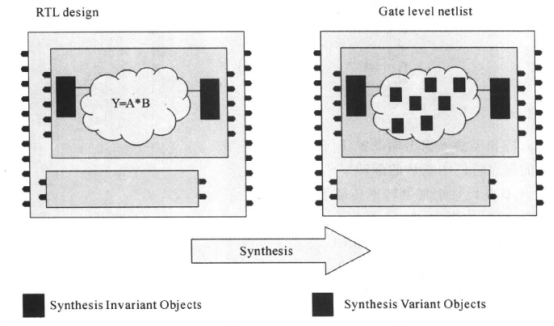

前面介绍了无向量分析法进行功耗分析,在介绍一下使用SAIF文件的方法进行功耗分析之前,我们先来介绍一下综合不变物体和综合变化物体的概念,下图为一个电路的RTL设计和门级设计:

根据定义,在综合前和综合后,设计中的寄存器数目和寄存器的结构是不变的,输入/输出端口和层次边界是不变的,设计中的黑盒子是不变的。这些不变的物体称为综合不变物体(Synthesis Invariant Objects,有时候也叫综合不变对象)。设计中大部分的组合电路生成与设计约束有很大的关系,不同的约束产生不同的组合电路。这些变化的物体称为综合变化的物体(Synthesis Variant Objects)。由于SAIF文件中涉及这两个概念,这里先进行介绍。

介绍完这两个概念之后,下面我们就来了解一下使用SAIF进行功耗分析。SAIF文件当做翻转率输入文件的方法有两种方式,也就是说利用SAIF进行功耗分析有两种方法——对RTL级的电路仿真后得到的SAIF文件(称为RTL backward SAIF) 以及 对门级网表的电路仿真后得到的文件(称为Gate backward SAIF)。下面逐个进行具体介绍。

(3)SAIF--RTL BACK分析法

RTL backward SAIF文件是通过对RTL代码进行仿真得到的,当设计很大的时候,门级仿真时间就会很长,这时候就可以使用这种方法进行分析。使用这种方法进行分析功耗的速度比较快,但是进度不够门级仿真SAIF文件的高。

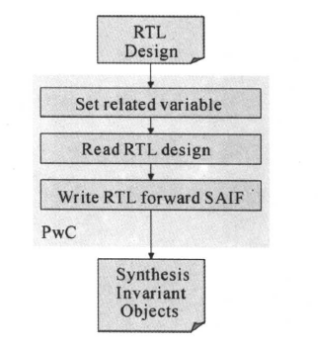

①RTL forward SAIF文件

RTL forward SAIF文件是记录RTL设计中综合不变物体的开关行为文件,可以简单地理解:RTL forward SAIF文件简要地记录了综合不变物的翻转率。RTL backward SAIF文件的产生需要RTL forward SAIF文件,因此我们首先需要产生RTL forward SAIF文件。产生RTL forward SAIF文件的流程如下:

RTL forward SAIF文件是由power compiler (包含在design compiler中)产生的,根据流程,我们知道,主要设置一些变量,然后读入RTL设计(RTL.v设计),接着读出SAIF文件就可以了。相应的脚本如下所示:

set power_preserve_rtl-hier_names true

read_verilog "sub.v top. v"

rtl2saif -output fwd_ rtl.saif

②RTL backward SAIF文件的产生

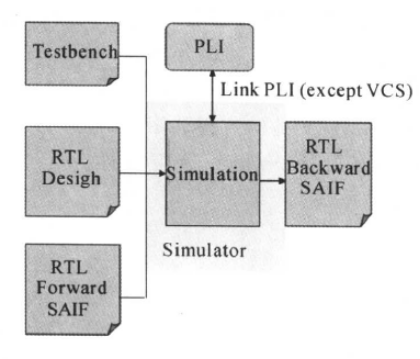

下面是产生RTL backward SAIF文件的流程:

从上图中,我们知道,产生RTL backward SAIF文件,需要在仿真器输入testbench测试平台文件、RTL.v设计、RTL forward SAIF文件,然后使用VCS产生RTL forward SAIF文件时,需要在testbench调用PLI监测节点的翻转率。下面我们就来介绍一下这几个部分。

·首先是PLI。使用VCS产生SAIF文件,需要用到程序设计语言接口(programming language interface,PLI)。通过PLI监测节点的翻转,得到节点的翻转率。主要需要下面的系统任务:

$set_gate_level_monitoring ( on|off|rtl_on);

$set_toggle_region (obj);

$read_ rtl_ saif(rtl_saif_file_name,tb_pathname);

$read_ lib_ saif(lib_saif_file_name);

$toggle_start;

$toggle_stop;

$toggle_reset();

$toggle_report(file_name,type,unit);

· RTL.v就是设计源文件了,然后RTL forward SAIF文件在前面也讲过了,这里就从略。

· 最后是testbench。testbench中调用RTL设计、调用一下上述的PLI系统函数、调用RTL forward SAIF文件等。一个简单的示例testbench文件如下所示:

module testbench;

top instl (a, b, c,s);//例化顶层设计

initial begin

$read_rtl_saif ("myrtl.saif")

$set_toggle_region (u1);

$toggle_start;

#120 a=0;

#STEP in_a=temp_in_a;

······

$toggle_stop;

$toggle_report("rtl.saif",1.0e-9,"top");

end

endmodule

上面的测试平台中,用了系统任务程序$read_rtl_saif ("myrtl. saif"),该命令读入综合不变物体文件——RTL forward SAIF。因此,仿真时,仿真器仅仅监视这些综合不变物体的开关行为。向量中$set_toggle_region (u1)命令选择要监视的模块。$toggle_start和$toggle_stop命令用于控制监视的起始和终止时间。$toggle_report("rtl. saif",1. 0e-9,"top")命令输出SAIF信息到指定的文件。

一起都准备就绪了,下面就可以使用VCS运行仿真:

vcs -R rtl. v testbench. v

注意,这里我们进行的是RTL设计文件的仿真,仿真完成后,就可以得到rtl.saif 文件,这个文件就是RTL backward SAIF文件。

|