【Vivado使用误区与进阶】在Vivado中实现ECO功能-1

|

- UID

- 1066743

|

【Vivado使用误区与进阶】在Vivado中实现ECO功能-1

如何利用Tcl在已完成布局布线的设计上对网表或是布局布线进行局部编辑,从而在最短时间内,以最小的代价完成个别的设计改动需求。什么是ECO

ECO指的是Engineering Change Order,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO的叫法算是从IC设计领域继承而来,其应用在FPGA设计上尚属首次,但这种做法其实在以往的FPGA设计上已被广泛采用。简单来说,ECO便相当于ISE上的FPGA Editor。

但与FPGA Editor不同,Vivado中的ECO并不是一个独立的界面或是一些特定的命令,要实现不同的ECO功能需要使用不同的方式。

ECO的应用场景和实现流程

ECO的应用场景主要包含:修改cell属性、增减或移动cell、手动局部布线。还有一些需要多种操作配合的复杂场景,例如把RAM(或DSP)的输出寄存器放入/拉出RAMB(或DSP48)内部,或是把设计内部信号接到I/O上作调试probe用等等。

针对不同的应用场景,Vivado中支持的ECO实现方式也略有区别。有些可以用图形界面实现,有些则只能使用Tcl命令。但通常可以在图形化界面上实现的操作,都可以改用一条或数条Tcl命令来实现。

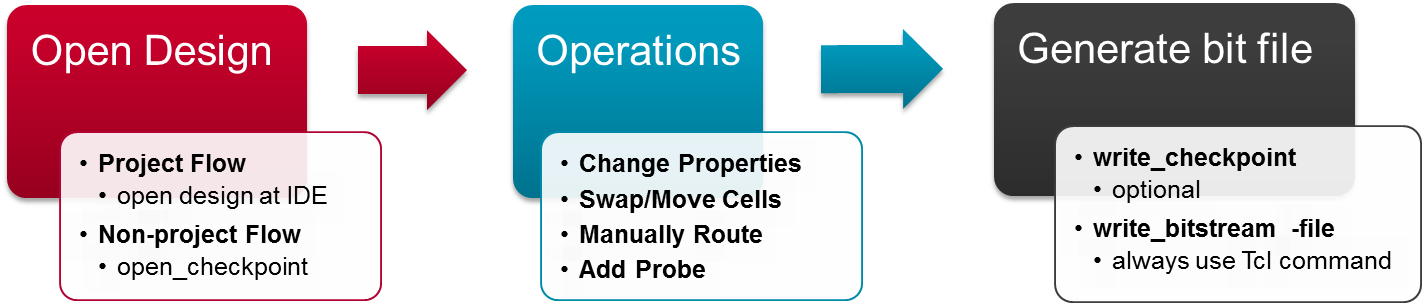

ECO的实现流程如下图所示:

第一步所指的Design通常是完全布局布线后的设计,如果是在工程模式下,可以直接在IDE中打开实现后的设计,若是仅有DCP文件,不论是工程模式或是非工程模式产生的DCP,都可以用open_checkpoint命令打开。

第二步就是ECO的意义所在,我们在布局布线后的设计上进行各种操作,然后仅对改动的部分进行局部布局/布线而无需整体重跑设计,节约大量时间的同时也不会破坏已经收敛的时序。

第三步就是产生可供下载的bit文件了,此时必须在Tcl Console中或是Tcl模式下直接输入命令产生bit文件,而不能使用IDE上的“Generate Bitstream”按钮。原因是后者读到的还是ECO前已经完成布局布线的原始设计,生成的bit文件自然也无法使用。

ECO的实现流程

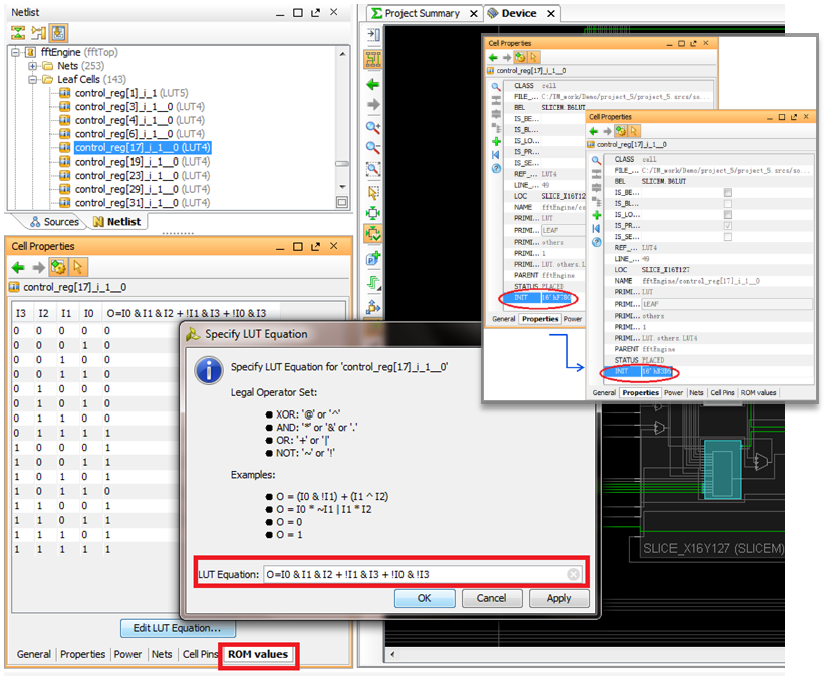

绝大部分的属性修改都能通过IDE界面完成,如下图所示:

比如要修改寄存器的初值INIT或是LUT的真值表,用户只需在Vivado IDE中打开布局布线后的设计(Implemented Design),在Device View中找到并选中这个FF/LUT,接着在其左侧的Cell Properties视图中选择需要修改的属性,直接修改即可。

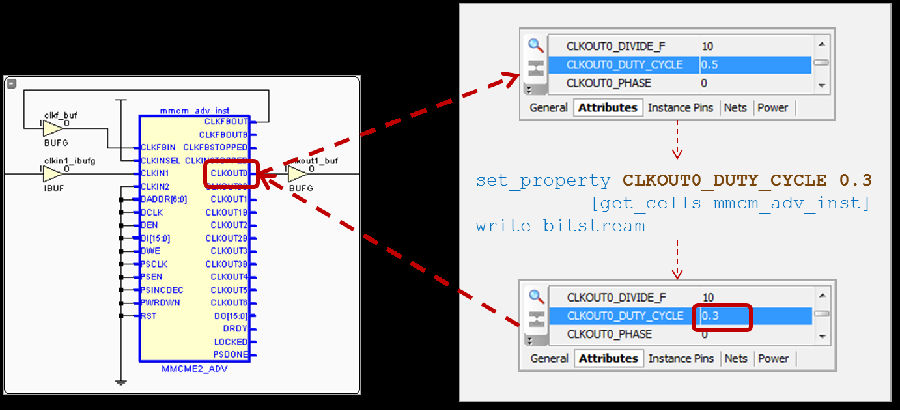

除了对FF/LUT的操作外,很多时候我们需要对MMCM/PLL输出时钟的相移进行修改。对于这种应用,用户也无需重新产生MMCM/PLL,与上述方法类似,可以在布局布线后的Device View上直接修改。

|

|

|

|

|

|