|

- UID

- 1029342

- 性别

- 男

|

本实验是数码管、按键、分频的综合实验,要求:用硬件描述语言verilog设计一个具有时、分、秒计数显示功能,以24小时循环计时的时钟电路,带有一键清零、以及秒、分、时校准的功能。下图是本设计的系统框图:

24小时计时时钟电路是对系统时钟进行分频到1Hz,下面是流程图:

按键控制模块中包括:清零键(clr)、设置键(set)、模式选择键(mode)。当清零键按下,时钟电路清零,数码显示零。设置键跟模式选择一起使用,对电路进行校准。各种模式的状态图如下:

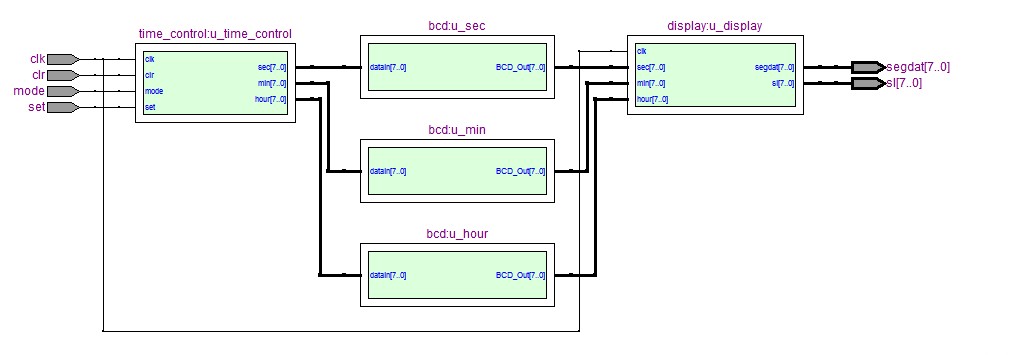

当这些都准备好了,你就开始你的工程吧,下面是整个工程的RTL视图:

以下是核心源码:

module clock(

clk,

mode,set,clr,

segdat,sl

);

input clk;

input mode,set,clr;

output segdat,sl;

wire[7: 0] segdat,sl;

wire[7: 0]sec,min,hour;

wire[7: 0]BCD_sec,BCD_min,BCD_hour;

//时钟控制模块例化

time_control u_time_control(

.mode(mode),

.clr(clr),

.clk(clk),

.set(set),

.sec(sec),

.min(min),

.hour(hour)

);

//秒BCD码例化

bcd u_sec(

.datain(sec),

.BCD_Out(BCD_sec)

);

//分钟BCD码例化

bcd u_min(

.datain(min),

.BCD_Out(BCD_min)

);

//小时BCD码例化

bcd u_hour(

.datain(hour),

.BCD_Out(BCD_hour)

);

//数码管显示例化

display u_display(

.clk(clk),

//.rst_n(rst_n),

.sec(BCD_sec),

.min(BCD_min),

.hour(BCD_hour),

.segdat(segdat),

.sl(sl)

);

endmodule

module time_control(

mode,clr,clk,set,

sec,min,hour

);

input mode,clr,clk,set;

output sec,min,hour;

reg[1:0] state;

reg [7:0] sec,min,hour; //秒和分处理寄存器 |

|