Xilinx的千兆以太网解决方案

一、Xilinx的千兆以太网解决方案

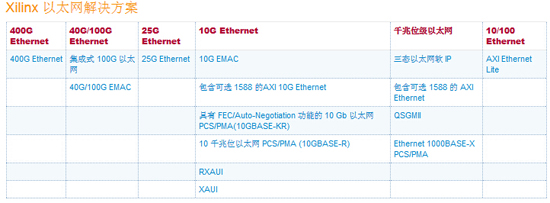

1)IP的支持

Xilinx 提供了可参数化的10/1Gbps以太网媒体访问控制器功能LogiCORE解决方案。该核设计用来同最新的Virtex-5、Virtex-4和 Virtex-II Pro平台FPGA一起工作,并可以无缝集成到Xilinx设计流程中。吉比特级以太网媒体访问控制器核(GEMAC)是针对1Gb/s(Gbps)以太 网媒体访问控制器功能的可参数化的LogiCORE IP解决方案。GEMAC核的设计符合 IEEE 802.3-2002规范。GWMAC核支持两个PHY端接口选项:GMII或RGMII。并且,Xilinx 全面的1Gb/s以太网解决方案包含吉比特MAC和PCS/PMA IP核产品。Xilinx吉比特以太网MAC解决方案还包括带有内置处理器本地总线(PLB)接口(PLB GEMAC)的配置。该配置通过Xilinx嵌入式开发套件(EDK)提供。GEMAC LogiCORE IP可以实现与1000 Base-X PCS/PMA或SGMII核的无缝集成,并提供3种选项用来与PHY器件接口:1000 BASE-X或10位接口(TBI)或SGMII。

GEMAC核非常适合开发高密度吉比特级以太网通信和存储设备,其关键特性有:

单速全双工11 Gbps MAC控制器;

设计符合IEEE 802.3-2002规范;

具有最小缓冲的直通操作,以最大限度地实现客户端接口的灵活性;

通过可选的独立微处理器中的接口进行配置和监控;

直接与以太网统计数据核接口,以便实现功能强大的统计数据收集;

通过MAC控制暂停帧实现对称的或非对称的可选的流程控制;

VLAN帧的可选技术支持符合IEEE 802.3-2002规范的要求;

支持任意长度的“jumbo帧”(可选);

可选的地址滤波器,具有数量可选的地址表输入。

2)相应的开发板套件

Xilinx 提供的千兆以太网开发套件为Virtex-5 ML505/ML506开发板(使用的FPGA芯片为:XC5VLX50T-1FF1136),该开发板支持10/100兆、1/10吉以太网,加上 Xilinx公开的基于ML505/506的设计,可为基于以太网开发的设计提供全方位的参考。此外,ML505/506还具备SFP、PCI E、SATA以及SMA接口等其余吉比特接口,是学习和研发高速连接设备的理想平台。

二、基于FPGA的千兆以太网MAC控制器实现方案

整体设计方案

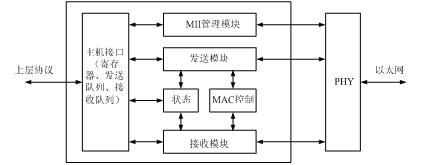

以太网控制器的FPGA设计工作包括以太网MAC子层的FPGA设计、MAC子层与上层协议的接口设计以及MAC与物理层(PHY)的MII接口设计。 该以太网控制器的总体结构设计框图如图10-30所示。整个系统分为发送模块、接收模块、MAC状态模块、MAC控制模块、MII管理模块和主机接口模块 六部分。发送模块和接收模块主要提供MAC帧的发送和接收功能,其主要操作有MAC帧的封装与解包以及错误检测,它直接提供了到外部物理层芯片的并行数据 接口。在实现中物理层处理直接利用商用的千兆PHY芯片,主要开发量集中在MAC控制器的开发上。

图1 以太网控制器的结构设计框图

MAC 控制模块则用于执行全双工模式中的流量控制功能。MAC状态模块可用来监视MAC操作过程的各种状态信息,并作修改。MII管理模块提供了标准的IEEE 802.3介质独立接口,可用于连接以太网的链路层与物理层。主机接口则提供以太网控制器与上层协议(如TCP/IP协议)之间的接口,以用于数据的发 送、接收以及对控制器内各种寄存器(控制、状态和命令寄存器)的设置。

三、Xilinx 千兆以太网MAC IP Core

1.GMAC IP Core的应用场景和架构

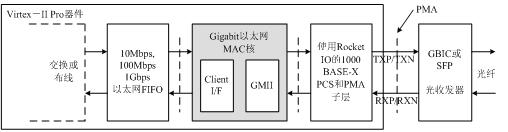

Xilinx 提供了三态以太网MAC控制器的IP Core,可实现单条吉比特以太网链路,通过交换机或路由器可与任意以太网端口相连。由于MAC控制器的速率很高,底层传输必须依赖Rocket I/O,在客户端还需要利用FIFO来交换数据,其完整的设计方案如图10-35所示。

图6 千兆以太网MACIP Core的应用场合示意图

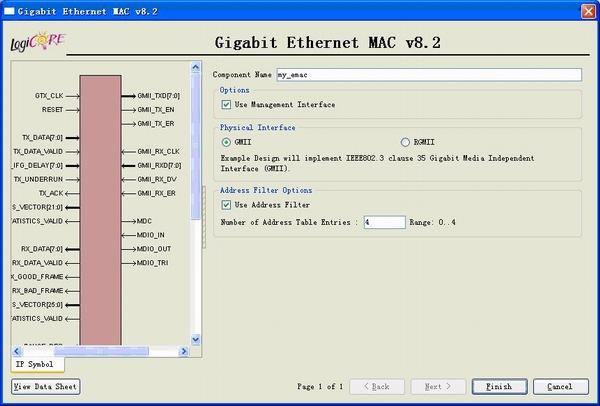

2.GMAC IP Core的配置界面和接口信号

图7 千兆以太网MACIP Core的配置界面

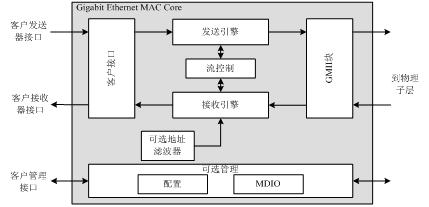

千兆以太网MACIP Core的配置界面如图10-36所示。GEMAC控制器所实现的主要功能如图10-37所示,包括发送引擎、接收引擎、流控制、GMII接口、客户发送接口、客户接收接口以及客户管理接口。

图8 千兆以太网MACIP Core的主要功能示意图

四、 本章小结

高速串行传输技术是FPGA未来的三大应用领域之一,本章主要介绍了Xilinx公司的Rocket I/O解决方案。首先给出高速传输的背景,指出串行方式是吉比特以及更高速率链路的必然选择。其次,给出了吉比特串行传输的通用架构,为后文做好铺垫。接 着重点介绍了Xilinx公司Rocket I/O的系统组成、相关协议、时钟设计方案、开发要素以及Rocket I/O的使用方法。最后说明了千兆以太网MAC控制器IP Core的使用方法。读者需要注意的是Rocket I/O是Xilinx高端FPGA中的内嵌组件,和DCM、硬核乘法器、块RAM等的使用方法是一样的,可通过IP Core调用。高速传输是一种新技术,开发难度较大,本章只是介绍了其中的主要核心部分和基本原理,还需要读者阅读大量的文献和实际操作才能熟练开发相关系统。

文章详情:Xilinx的千兆以太网解决方案

Altera的千兆以太网解决方案

1 IP核的支持

Altera提供了可参数化的千兆以太网megacore解决方案。该方案可在Altera的Arria GX,CycloneII,CycloneIII系列FPGA上工作,可配置使其包含MAC,PCS,PMA模块中的一种或多种,配置选择及相应的接口标准。

千兆以太网IP核的功能描述如下:

(1)支持IEEE 802.3标准。

(2)10/100/1 000 Mb,s以太网媒体访问控制支持半双工和全双工工作模式。

(3)多通道MAC,支持最多24端口。

(4)以太网物理层编码子层1000BASE一X/SGMII标准的自协商。

(5)接口使用方便。

对于千兆以太网控制器的实现,采用表第l行的配置。吉比特级以太网媒体控制器核(GEMAC)是针对1 Gb/s以太网媒体访问控制器功能的可参数化的megacore解决方案。

2 基于FPGA的千兆以太网MAC控制器实现方案

2.1 整体设计方案

以太网控制器的FPGA设计工作包括以太网MAC子层的FPGA设计,MAC子层与上层协议的接口设计以及MAC与物理层(PHY)的GMII接口设计。该以太网控制器的总体结构设计框图如图1所示,整个系统分为MAC模块,主机接口模块和管理数据输入输出模块。其中,MAC模块主要执行在全双工模式下的流量控制,MAC帧实现发送和接收功能,其主要操作有MAC帧的封装与解包以及错误检测,直接提供了到外部物理层器件的并行数据接口,物理层处理直接利用商用千兆PHY器件,主要开发集中在MAC控制器的研究。

管理数据输入输出模块提供了标准的IEEE802.3介质独立接口,可用于连接以太网的链路层和物理层。主机接口则提供以太网控制器与上层协议(如TCP/IP协议)之间的接口,用于数据的发送、接收以及对控制器内各种寄存器的设置。

2.2 接口描述

整个系统模块间的接口连接如图2所示。其中,PCS和PMA分别代表物理层的物理编码子层和物理介质接入层。

(1)通过MII/GMII接口提供了与以太网物理层(PHY)设备的无缝连接。

(2)吉比特模式下支持RGMII接口。

(3)可选择的管理数据输入/输出模块为以太网PHY提供管理信息。

(4)为用户提供基于Aalon—ST的8 bit/32 bit接口。

(5)可选择的集成物理介质介入模块。

2.3 千兆以太网IP核

Altera提供三态以太网MAC控制器IP核,可实现单条或多条吉比特以太网链路,通过交换机或路由器可与任意以太网端口相连。其配置界面如图3所示。

整个配置界面可将IP核配置为所需模式并进行IP核参数设置,将IP核设置为千兆以太网MAC模块,内部提供FI—FO模块。可选的PCS模块由PHY器件提供,这个界面分为4个配置页面,描述如下:

Core Configuration:核配置选项,配置以太网功能模块,是否包含PCS模块、FIFO模块,配置接口类型、端口数等;

MAC Options:MAC配置选项,配置MAC模块功能;

FIFO Options:FIFO存储器选项,可设置FlFO存储器类型以及存储器数据长度;

PCS/SGMII Options:物理介质接入层模块配置页面,配置物理层。

相应的接口信号包括:控制接口信号,复位信号,MAC系统端信号(包括接收接口信号和发送接口信号),MAC以太网端信号(包括GMII模块信号和PHY管理接口信号)。

表1中描述了MAC以太网端GMII模块信号、接口信号,其余信号参考千兆以太网用户手册。GMII模块的接收信号一般直接连到PHY器件,负责与PHY器件的数据交互,其信号与PHY器件接口一一对应,如表1所列。

4 物理层(PHY)器件

Ahera公司的千兆以太网MAC核默认支持的物理层器件有支持10/100 Mb/s的National DP83848C,支持10/100/1 000 Mb/s的National DP83865,Marveil 88E1145以及支持双物理层和10/100/l 000 Mb/s的Marvell 88E1111。在此,选择National DP83865为PHY器件。

MAC核与吉比特PHY器件通过GMII接口的连接如图4所示。

DP83865是National Semiconductor公司的全特性物理层收发器,集成了PMD子层以支持10BASE-T,100BASE-TX和1000BASE-T以太网协议,具有超低功耗,3.3V或2.5VMAC接口。

5 开发环境

利用Ahera强大的SOPC Builder系统开发工具和Quar-tusII软件设计,基于QuartusII和niosII的SOPC设计流程如图5所示,SOPC开发流程比 FPGA的开发流程(细线框)多增加处理器及其外设接口的定制步骤和软件开发步骤(粗线框)。这些新增加的步骤在SOPC Builder,niosII IDE工具的协助下能够轻松完成。

6 结语

使用千兆网系统可直接将处理的高速信号从网口发送给远端处理计算平台,节省功率放大器和高频电缆等,减少投入,加强系统的集成性和可靠性,更便于设计人员的调试,且接口更具通用性和扩展性。

近年来,随着以太网技术的进一步发展和完善,特别是通信速率的提高和交互技术的应用,使得以太网技术应用于现场控制领域成为可能,这对工业控制 网络产生了新的影响。从目前的趋势来看,以太网己经进入了现场控制级,但是已有的现场总线仍将继续存在,工业以太网只能占领一定的市场。

从现实来看,以太网扩展了现有的系统,但是现场总线不可能完全被工业以太网替代,后者的潜力巨大,其应用领域一定会不断扩大。所以,将现场总线与以太网 结合,从而实现底层生产与上层管理的紧密集成,已经成为一种趋势。CAN总线作为国际上应用最广泛的现场总线之一,在我国也得到了很广泛的应用,该设计以 CAN总线作为工业现场总线,实现其与以太网的互联。

1 硬件结构

目前,对于 CAN和以太网相连的嵌入式网关设计主要有两种方法:一种是低档MCU加接口芯片的设计方法,另一种是高档MCU加EOS(实时多任务操作系统)再加接口 芯片的设计方法。因CAN只采用了ISO/OSI参考模型的一、二层,协议相对简单,比较适合用于低成本、速率要求不高的离散控制系统。从合理的成本和有 效利用处理能力这两方面考虑,该设计采用低档MCU加接口芯片的方法,其硬件框图见图 1。

1.1 主控芯片及以太网接口模块

根据要求,该系统选择了性能价格比较高的Atmel公司生产的AT89C55单片机。它是面向测控对象和嵌入式应用的,所以它的体系结构以及CPU、指 令系统、外围单元电路都是按照这种要求专门设计的。它内部带高达20 KB的FLASH程序存储器,AT89C55完全兼容8051指令集,片上FLASH方便了使用者进行在线编程,工作速率最高可达33 MHz,256 B的内部RAM,32个可编程的I/O口,3个16位的定时/计数器,8个中断源,支持低功耗的空闲工作模式。以太网接口选用的是RTL8019AS芯 片,它是由Realtek公司生产的一种高度集成的以太网控制器,能实现以太网媒介访问层(MAC)和物理层(PHY)的全部功能。RTL8019AS内 部有两个RAM区域:一是16 KB,地址为0x4000~0x7fff,要接收和发送数据包必须通过DMA读写RTL8019AS内部的16 KB的RAM,它实际上是双端口RAM,即有两条总线与其连接,一条总线用于RTL8019AS读/写或写/读该RAM,即本地DMA;另一条总线用于单 片机读或写该RAM,即远程DMA;二是32个字节,地址为0x0000~0x001F,用于存储以太网物理地址。主控芯片和以太网接口芯片的硬件接口原 理图见图2。值得注意的是由于以太网的包最大可以超过1 500个字节,AT89C55的片内RAM只有256个字节,因此无法存储这么大的包,所以这里扩展了一个32 KB的外部RAM,这样同时也能提高单片机的数据传输速度。

1.2 CAN接口模块

组成CAN系统的主要器件是CAN控制器和收发器。该设计中,CAN接口模块选用SJA1000芯片和PCA82C250芯片。SJA1000是一个独 立的CAN控制器,它是Philips公司另一个CAN控制器PCA82C200的替代产品,且增加了一种新的工作模式(Peli CAN),这种模式支持CAN 2.0B协议。SJA1000主要完成CAN的通信协议,实现报文的装配和拆分、接收信息的过滤和校验等。

PCA82C250是CAN控制器与物理总线之间的接口,主要用于增强系统的驱动能力。采用收发器的系统中,节点数至少可以达到110个,同时还具有降低射频干扰(RFI)和很强的抗电磁干扰 (EMI)能力。在处理这部分电路时,有几个地方要特别注意:

(1)晶振电路的问题。89C55和SJA1000都应该有各自独立的晶振电路,不能够用SJA1000的时钟输出信号CLKOUT来驱动单片机。

(2)复位引脚的问题。虽然SJA1000的复位是低电平,但不能通过一个非门直接连接单片机的复位引脚。一般对解决复位引脚问题有两种方式:第一种是 使用单片机的I/O引脚控制SJA的复位引脚,其好处是单片机可以完全控制SJA的复位过程;第二种是采用适当的复位芯片,为了降低成本,该设计采取的是 第一种方法。

(3)RX1引脚的电位必须维持在约0.5 VCC上,否则将不能形成CAN协议所要求的逻辑电平。

(4)一定要注意电缆的终端阻抗匹配,它直接影响CAN总线是否能正常工作和网络性能。CAN接口模块的硬件电路图见图3,在PCA82C250的RS脚上接有一个斜率电阻R,可根据总线通信速度适当调整电阻的大小。

2 通信模块软件设计

2.1 SJA1000驱动程序的实现

SJA1000驱动程序是由SJA的初始化函数、发送函数、接收函数组成的,图4所示为其流程图。

(1)SJA1000的初始化。SJA1000在系统上电、硬件复位或主控制器发出复位命令后需要进行初始化,以设定它的工作模式、通信速率、输出控制 方式和标识符屏蔽格式等重要参数。CAN控制器SJA1000的初始化只能在复位模式下才能完成。程序的流程图如图4所示。

首先程序检测CAN接口是否正常工作,即向SJA1000的测试寄存器写入并读出,校验其结果是否一致,如果结果一致则进入复位模式进行初始化设置。在初始化的过程中,如果对某个寄存器的设置超过规定的时间还未完成,则认为初始化失败,初始化程序自动发送错误信号。

(2)数据的发送与接收。SJA1000芯片有一个报文发送缓冲区和两个报文接收缓冲区,用于CAN报文传送。数据从CAN控制器SJA1000发送到 CAN总线首先是由CAN控制器自动完成的,发送数据程序把数据存储区中待发送的数据取出,组成信息帧,并将主机的ID地址填人帧头;然后将信息帧发送到 CAN控制器的发送缓冲区;最后启动发送命令即可。信息从CAN总线到CAN接收缓冲区也是由CAN控制器自动完成的。接收程序只需从接收缓冲区读取要接 收的信息,并将其存储在数据存储区即可。

2.2 RTL8019AS驱动程序的实现

RTL8019AS的驱动程序和SJA的驱动程序一样,有3种功能:芯片初始化、收包、发包。

(1)RTL8019AS的初始化。RTL8019AS的初始化过程比较复杂,但十分重要,它决定了通信过程中的一些重要参数。如设置相关工作模式的寄存器,分配和初始化接收及发送缓冲区,初始化网卡接收地址等,其流程图见图5所示。

(2)数据的发送与接收。因为在RTL8019AS的初始化程序中已经完成了以太网的物理地址设置,并指定了发送缓冲区起始页面地址寄存器TPSR。此 外,RTL8019AS的CRC校验自动生成器也被使能,所以RTL8019AS的数据包发送程序相对要简单。在数据包的发送过程中,AT89C55只要 通过远程DMA将待发送的数据包写至RTL8019AS片内SRAM的发送缓冲区,并启动发送过程即可。

在接收数据包时,有查询和中断两种方式,鉴于AT89C55的处理能力有限,在该设计中采用查询方式,根据判断CURB==BNRY+1,可以判断是否收到新的数据包,如果有则通过DMA读操作从网卡芯片RAM读出数据。

2.3 网关协议转换流程

嵌入式网络接口实现两种网络的互连。当以太网应用层有数据要发送到CAN节点时,首先将数据发送到网关,由以太网控制器协议转换模块解析完整的CAN协 议数据包,通过CAN控制器发送到CAN总线。反之,当CAN设备有数据要发送到用户层时,首先将数据发送到透明网关,由CAN控制器协议模块将完整的 CAN协议数据包存放在缓冲区,再通知主控芯片,由它调用以太网控制协议转换模块,将完整的 CAN协议数据包作为应用层数据封装起来,再发送到以太网的应用层。

3 结 语

这里介绍的是一种低成本、高可靠性、快捷的CAN以太网网关的硬件、软件设计方案,通过实际应用证明,该设计可以作为CAN总线节点的一个模块,能够与仪器仪表等设备相结合,使其具有网络通信的能力,比较同类产品的设计,该设计能大大提高其性价比。 |