本文主要针对S3C2440分析

S3C2440的主时钟源来自外部晶振(XTIPLL)或外部时钟(EXTCLK)。S3C2440有两个PLL(phase locked loop)一个是MPLL,一个是UPLL。MPLL用于CPU及其他外围器件,UPLL用于USB。

1,MPLL, 用于产生FCLK, HCLK, PCLK三种频率, 这三种频率分别有不同的用途:

FCLK是CPU提供的时钟信号。

HCLK是为AHB总线提供的时钟信号, Advanced High-performance Bus,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器, DMA 等。从S3C2440的DataSheet里可以看到,S3C2440最大支持400MHz的主频,但是这并不意味着一定工作在400MHz下面,可以通过设定MPLL, UPLL寄存器来设定CPU的工作频率。

PCLK是为APB总线提供的时钟信号,Advanced Peripherals Bus,主要用于低速外设,比如看门狗,UART控制器, IIS, I2C, SDI/MMC, GPIO,RTC and SPI等。

2,UPLL,专门用于驱动USB host/Device。并且驱动USB host/Device的频率必须为48MHz。

如果要设置MPLL和UPLL,要注意它们的先后顺序,MPLL和UPLL的设定是有前后顺序的,必须先设定UPLL,然后才能设定MPLL,而且中间需要大约7个空指令(NOP)的间隔。

S3C2410 CPU默认的工作主频为12MHz(Fin),使用PLL电路可以产生更高的主频供CPU及外围器件使用。

通过MPLL会产生三个部分的时钟频率:FCLK、HCLK、PLCK。FCLK用于CPU核,HCLK用于AHB总线的设备(比如SDRAM),PCLK用于APB总线的设备(比如UART)。

时钟电路相关寄存器总共有7个,下面分别介绍。

MPLLCON(0X4C00 0004)和UPLLCON(0X4C00 0008)

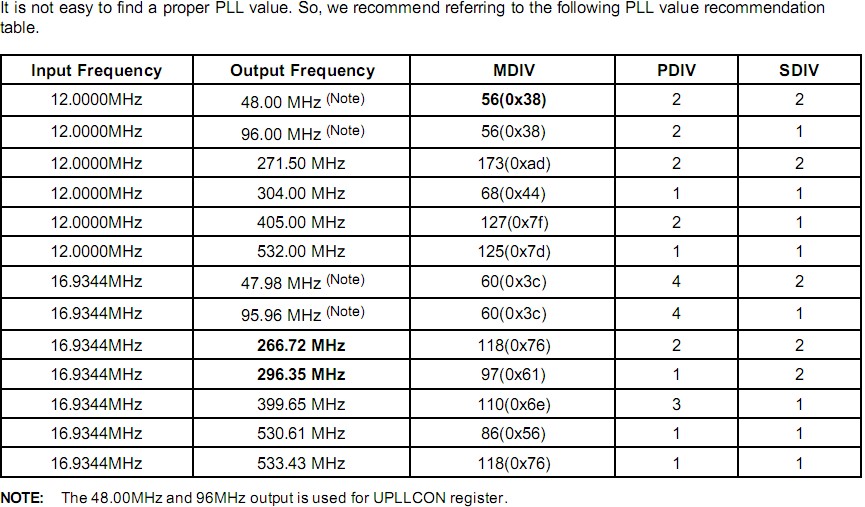

这两个寄存器用来设置主锁相环产生的时钟和USB锁相环产生的时钟。

/*

Mpll = (2 * m * Fin) / (p * 2s)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

Upll = (m * Fin) / (p * 2s)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

MDIV =PLLCON[19:12]; PDIV=PLLCON[9:4]; SDIV=PLLCON[1:0];

*/

P,M范围:1<=P<=62,1<=M<=248

注意:MDIV[19:12],PDIV[9:4],SDIV[1:0],当设置MPLL和UPLL值的时候,需要先设置UPLL再设置MPLL。

例如:MPLLCON = (92<<12) | (1<<4) |(1);//FCLK=400M

这里MDIV=92,PDIV=1,SDIV=1,那么m=100,p=3,s=1,且Fin=12M,所以FCLK=400M

所以u-boot的设置代码如下:

- #define CLKDIVN 0x4C000014 /* clock divisor register */

- #define CLK_CTL_BASE 0x4C000000 /* 时钟控制寄存器基址*/

- #define MDIV_405 0x7f << 12 /* MPLL MDIV[19:12] */

- #define PSDIV_405 0x21 /* MPLL PDIV[9:4] + SDIV[1:0] */

- #define MDIV_200 0xa1 << 12 /* UPLL */

- #define PSDIV_200 0x31 /* UPLL */

- ……………………

- # if defined(CONFIG_S3C2440)

- /* FCLK:HCLK:PCLK = 1:4:8 */

- ldr r0, =CLKDIVN

- mov r1, #5

- str r1, [r0]

- mrc p15, 0, r1, c1, c0, 0 /*read ctrl register*/

- orr r1, r1, #0xc0000000 /*Asynchronous*/

- mcr p15, 0, r1, c1, c0, 0 /*write ctrl register*/

- /*now, CPU clock is 405.00 Mhz 查datasheet*/

- mov r1, #CLK_CTL_BASE /* */

- mov r2, #MDIV_405 /* MPLL_405mhz */

- add r2, r2, #PSDIV_405 /* MPLL_405mhz*/

- str r2, [r1, #0x04] /* MPLLCON tekkaman */

- #else

- /* FCLK:HCLK:PCLK = 1:2:4 */

- /* default FCLK is 12 MHz !*/

- ldr r0, =CLKDIVN

- mov r1, #3

- str r1, [r0]

- mrc p15, 0, r1, c1, c0, 0 /*read ctrl register */

- orr r1, r1, #0xc0000000 /*Asynchronous */

- mcr p15, 0, r1, c1, c0, 0 /*write ctrl register */

- /*now, CPU clock is 202.8 Mhz */

- mov r1, #CLK_CTL_BASE

- mov r2, #MDIV_200 /* MPLL_200mhz */

- add r2, r2, #PSDIV_200 /* MPLL_200mhz */

- str r2, [r1, #0x04]

- # endif

- #endif /* CONFIG_S3C2400 || CONFIG_S3C2410|| CONFIG_S3C2440 */

附:

|