9.3FPGA系统设计的3种常用IP模块

FPGA的开发工具软件,如Quartus II、ISE等,一般都会提供一些经过验证的IP模块。这些IP模块是芯片厂家提供的,所以只能用于该厂家的FPGA芯片设计中。这些IP主要包括以下几类。

·算术类,如乘法器、加法器、除法器等。

·逻辑门类,如与门、或门、非门等。

·存储器类,如FIFO、RAM、ROM、移位寄存器等。

·I/O类,如双向IO、PLL、LVDS等。

·接口类,如以太网MAC、PCI接口控制器、高速串行收发器(SERDES)等。

·商业IP核,需要付费购买的。

以上的IP中,最常用的3个IP分别是片上存储器(RAM/ROM/FIFO),锁相环(PLL/DLL)和高速串行收发器(SERDES)。灵活使用这些IP,可以提升设计的性能,同时降低设计的复杂度。

IP模块的实现方式主要有3种:使用HDL代码描述、使用综合约束属性例化或类推、使用器件商的IP core生成器。

典型功能的IP core都可以通过这3种途径实现。其中前两种方法需要学习综合RAM、ROM、CAM等存储单元的Coding Style或约束属性,后一种方法非常方便、直接,建议初学者首先要掌握使用器件商IP core生成器设计RAM、ROM、CAM等存储单元的方法。

下面通过Quartus II工具分别介绍Altera的3种IP模块的使用方法。

9.3.1片上存储器的使用方法

片上存储器由内嵌于FPGA内部的逻辑资源(分布RAM和块RAM)搭建而成。搭建出来的这些片上存储器的调用方法与分立器件基本一致,但却为开发者省去了大量的PCB布线资源。在小容量的存储器设计中有着非常广泛的应用,同时这些片上存储器还常常用作数据缓冲及时钟域转换等工作。

首先来介绍片上FIFO 的使用方法。

1.FIFO

(1)打开宏模块向导管理器。

在Quartus II中,IP模块的生成都是通过“MegaWizard Plug-In Manager”(宏模块向导管理器)实现的,它可以通过如图9.9的“Tools”菜单打开。

(2)选择新建宏模块。

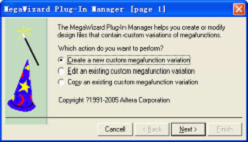

在宏模块向导管理器的第1页,选择新建一个自定义的宏模块,如图9.10所示。

图9.9宏模块向导管理器调用

图9.10新建宏模块

(3)选择宏模块。

在宏模块向导管理器的第2页,管理器为我们提供了支持的宏模块树形目录。通过在该目录中选择相应的宏模块实现调用。同时在这一页中还可以选择应用的FPGA器件系列和宏模块的描述语言,并使用用户自定义的模块名,如图9.11所示。

图9.11选择宏模块

在本例中,我们选择“LPM_FIFO+模块”进行实现。

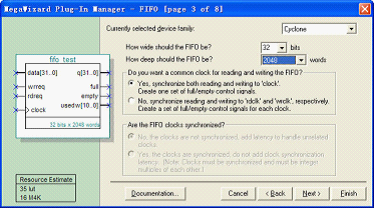

(4)设置FIFO宽度和深度。

在宏模块向导管理器(FIFO)的第3页,可以设置FIFO的深度和宽度,同时在本页的左下角会计算出实现这样一个深度和宽度的FIFO所消耗的FPGA资源,如图9.12所示。

图9.12设置FIFO深度和宽度

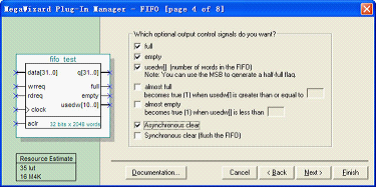

(5)设置FIFO的控制信号。

在宏模块向导管理器(FIFO)的第4页,可以设置FIFO的控制信号,包括满信号full、空信号empty、使用字节信号组usedw[ ]、几乎满信号almost full(可编程)、几乎空信号almost empty(可编程)、异步清零信号和同步清零信号。

通过选择是否打开这些信号来构造一个用户自定义的FIFO,如图9.13所示。

图9.13设置FIFO的控制信号

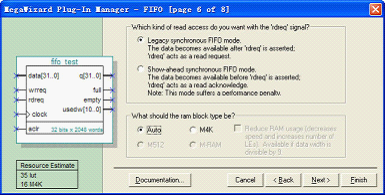

(6)设置FIFO的模式。

在宏模块向导管理器(FIFO)的第6页,可以设置FIFO的模式。分为Lagacy同步模式和Show-ahead同步模式。区别在于输出数据是在FIFO的读请求信号rdreq发出之前还是之后有效,用户可以根据需要进行选择,如图9.14所示。

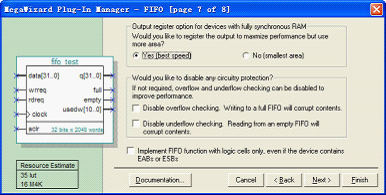

(7)设置FIFO的外部属性。

在宏模块向导管理器(FIFO)的第7页,可以设置FIFO的外部属性,包括输出寄存器使用最佳速度策略还是最小面积策略,数据溢出及读空状态下的保护机制,还可以强制只利用逻辑单元来构造FIFO,如图9.15所示。

图9.14设置FIFO的模式

图9.15设置FIFO的外部属性

(8)选择生成的FIFO模块文件。

在宏模块向导管理器(FIFO)的第8页,也就是最后一页,可以选择生成的FIFO模块文件。在Quartus II软件中,宏模块向导管理器可为FIFO生成7个文件,如图9.16所示。

图9.16选择生成的FIFO模块文件

图9.17打开工程添加/删除文件对话框 |