采用MAX II器件实现FPGA设计安全解决方案(2)

|

- UID

- 1029342

- 性别

- 男

|

采用MAX II器件实现FPGA设计安全解决方案(2)

解决方案的安全性

上电时,当FPGA的配置比特流由外部存储器传送至FPGA时,有可能被捕获。使用捕获的比特流来配置其他FPGA可以拷贝FPGA设计。

采用该解决方案,只有当MAX II器件的握手令牌与FPGA内部产生的数据相匹配时,FPGA用户设计才开始工作。由于被复制的设计在没有握手令牌时无法工作,因此保证了FPGA设计的拷贝安全性。用于产生握手令牌的MAX II器件具有非易失特性,关电时可保持其配置。

解决方案的安全性依赖于MAX II器件产生的握手令牌。要破解该方案,需要拷贝MAX II器件产生的全部令牌比特流,或者计算出编码器用于产生令牌的密钥。由于每次上电时,MAX II器件产生的握手令牌都不同,因此,拷贝全部比特流来破解该方案是不可能的。这在于采用了RNG,它在上电时产生不同的数值送给MAX II器件。

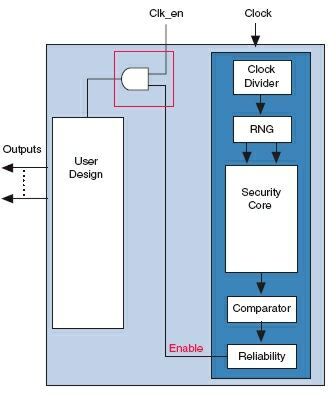

图4:支持安全方案的FPGA设计。

如果采用了成熟的加密算法,那么破解编码器使用的密钥将非常困难。而且,无法从外部看到编码器输入数据,只有一部分加密数据串行移出,更难实现纯文本攻击。纯文本攻击分析编码器的输入和输出数据,猜出密钥,实施攻击。因此,该解决方案保护了FPGA设计。

为保证该方案正常工作,安全模块的时钟应和FPGA用户设计的时钟一致,如图1所示。这样可以防止有人在Enable信号高电平时,禁用安全模块时钟。

本文小结

FPGA设计安全解决方案保护了Altera FPGA设计被拷贝(即使配置比特流被捕获)。在MAX II器件通过握手令牌验证前,禁止FPGA用户设计,实现了该解决方案。只有握手令牌与FPGA内部产生的数据匹配时,FPGA用户设计才被使能。该解决方案还保护了FPGA中的设计人员知识产权。 |

|

|

|

|

|