|

- UID

- 871057

- 性别

- 男

|

随着便携式设备的广泛使用,移动存储设备被广泛用于信息存储和传输。在目前诸多存储设备中,U盘凭借其体积小、容量大、携带方便、支持热插拔等诸多优点,得到了迅速的普及。而且随着USB技术的广泛应用,在各种SoC系统中集成USB功能也成为一种必然趋势。所以对SoC芯片中集成USB接口的研究开发,具有较高的实用价值。

文中通过分析USB协议,设计出了一种符合该协议的低速和全速的USB设备控制器,并将该控制器与8051CPU核,NandFlash,UDC_Control通过总线连接起来,组成了一个U盘SoC系统,并对此U盘SoC系统加以仿真验证。

1 系统的整体设计

现在的USB控制器主要有两种:带USB接口的单片机(MCU)和纯粹的USB接口芯片。纯粹的USB接口芯片仅处理USB通信,必须有一个外部微处理器来进行协议处理和数据交换。带USB接口的单片机从应用上又可以分成两类,一类是从底层设计专用于USB控制的单片机;另一类是增加了USB接口的普通单片机,这类USB控制器的最大好处在于开发者对系统结构和指令集非常熟悉,开发工具简单,但价格比较高,不利于产品升级和改型。

根据上述情况,文中介绍了一种U盘SoC设计:将CPU和USB CORE通过UDC_Control模块连接起来,再加上NandFlash模块,通过总线连接组成一个SoC系统。其整体框图如下图1所示。

2 模块的详细设计

2.1 USB CORE

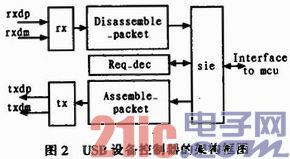

此模块为该设计的核心模块,实现USB1.1总线接口层设备控制器的功能,是本文设计的重点。USB设备控制器的架构框图如图2所示,rxdp、rxdm为从主机发送过来的信号,txdp、txdm为USB模块发送给主机的信号。其中MCU通过控制SIE来对USB设备进行控制。如图2所示,本设计分为6个模块。下面分别介绍各个模块。

2.1.1 rx模块

rx模块是总线接收模块,实现USB数据传输接收物理层的功能,把串行的USB数据去掉数据包头,进行NRZI解码,去掉填充位,并将串行的数据转换成并行的8位数据。然后将数据送往下一模块处理。本模块又分为dpll、解码和总线状态监测模块。如图3所示。

dpll模块用48 MHz的时钟把总线上传输的时钟和数据信号恢复出来。用48 MHz的时钟对总线上的数据信号进行采样,以去掉抖动,然后产生总线信号电平变化的指示信号change信号,change信号的改变可控制采样点,从而保证数据信号的采样点固定在每位数据信号的中央。

NRZI解码模块检测到同步头后,根据NRZI的原理,将rxdp和rxdp延后一拍的数据进行同或操作,得到的数据经过去填充位,串并转换后,送入解包模块。

总线状态监测模块监测总线的状态,置位suspend,resume,reset等状态指示信号。若Idle时间超过3ms时,就将suspend信号置高,在suspend状态时检测到总线信号变化时,将resume信号置高,若se0时间超过2.5μs时,就将reset信号置高。

2.1.2 解包模块

本模块接收从rx模块送过来的并行数据,按照USB数据包协议规范对接收的数据进行解释,并对数据做CRC校验,给出当前接收包的类型,根据不同类型的包的结构,从包中解出相应的信息送给下一模块。

2.1.3 req_dec模块

本模块对setup阶段USB的标准请求进行解释,提供和USB请求相关的信号给SIE模块,判断funetion和endpoint的地址是否合法。若标准请求中对某个端点所请求的操作和预定的不符,则会产生错误信号。

2.1.4 SIE模块

SIE(Serial Interface Engine)模块是USB CORE的核心模块,根据从解包模块传送过来的信号与从MCU传送过来的接口握手信号,按照USB的相关协议,产生打包模块的控制信号和MCU的控制信号,从而控制总线上的数据发送。 控制传输的实现:

SETUP阶段:从图4中可看出,当token_valid_i、Pid_setup、ep0_sel有效时,表明收到一个有效的令牌包,udc_as_o被拉高,表示开始数据传送,转入ctrl_setup_stage状态,此时cpu把device_bufok_i信号拉高,随后开始接收数据,在setup阶段8个字节的标准请求数据接收完成后,send_hdsk_pkt_o信号变高,表示数据接收正确,要求发送一个ACK的握手包。

DATA阶段:数据阶段是可选的,并且数据阶段的传送方向可以是IN或OUT。以IN为例来介绍,当Pid_in、token_valid_i、ep0_sel有效时,udc_as_o被拉高,表示开始数据传送,转入ctrl_in_stage_empty,接着转入ctrl_in_stage状态,CPU将device_bufok_i拉高,表示开始接收数据,等待数据传完后,send_hdsk_pkt_o信号变高,表示数据接收正确,并将toggle机制翻转,要求打包模块发送一个ACK的握手包。

STATUS阶段:STATUS阶段也分为STATUS IN和STATUS OUT两种情况。在STATUS OUT阶段,接受到HOST发送过来的空数据包后,状态机会将send_hdsk_pkt_o信号拉高,发送ACK包给HOST。其状态机同SETUP状态机类似。

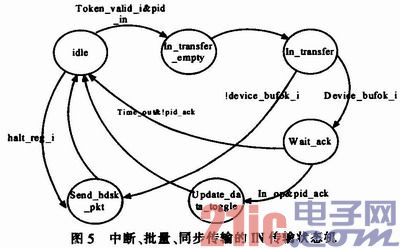

中断、批量、同步传输的IN实现:在硬件设计上,中断、批量和同步3种传输方式的处理都是一样的,只是在系统配置时,各传输方式对应的端点不同。下面以3种传输方式的IN传输来介绍。图5为3种传输方式的IN传输的状态机。

从上图可看出,在收到IN令牌后,状态机将tide_as_o拉高,表示开始传送数据,转入In_transfer_empty状态,再转入In_transfer状态,cpu若能传送数据,则把device_buf_ok_i信号置高,开始接收数据,等待数据传送完毕时,状态机会将send_data_pkt_o拉高,将此信号送至打包模块,从而将所需要的数据发送给HOST。

2.1.5 打包模块

本模块接收从SIE传来的控制信号,根据USB协议,产生所需要的包传送给发送模块。

2.1.6 tx模块

tx模块是总线发送模块。它将打包模块发送过来的包信息,进行并串转换,位填充,NRZI编码后,将数据发送给主机。此模块同rx模块类似,不再赘述。

2.2 8051CPU

此设计中的CPU为一个验证过的IP核。它包含:1个8位中央处理器、1个片内振荡器及时钟电路、4 KB ROM程序存储器、128B RAM数据存储器、可寻址64 KB外部数据存储器和64 KB外部程序存储器的控制电路、32条可编程的I/O线(4个8位并行I/O接口)、2个16位的定时,计数器、1个可编程全双工串行接口、5个中断源、2个优先级嵌套中断结构。将USB的通信请求接入到CPU的一个外部中断接口上,当USB的通信请求到来时,系统会产生一个中断,转入中断服务程序。

此外,还需要设计一个CPU的固件firmware,实现USBCORE的上电初始化过程(向UDC_Control中的控制寄存器和状态寄存器写入初始数据)、USB CORE中断处理并完成USB传输事务、使设备摆脱异常状态等功能。

2.3 UDC_Control

UDC_Control模块位于CPU和USB CORE之间,它完成CPU对USB通信的控制和数据的读写操作。UDC_CTRL模块中设有22个特殊功能寄存器,来完成USB通信。

USB_INT1和USB_INT2为中断寄存器,其各个位分别表示USB通信的9种中断请求(剩下的位为保留位),但USBCORE一次只能向CPU提供一个中断信号,这两个USB_INT寄存器供软件在进入中断后查询是USB的何种中断。EP0_CTRL、EP0_INFIFO_DATA、EPO_INFIFO_CNT、EP0_OUTFIFO_ DATA、EP0_OUTFIFO_CNT这5个寄存器都是与Endpoint0相关的,Endpoint0是由一个输入端点和一个输出端点组成,用来实现控制传输。所有支持USB标准请求和Class定义的请求都通过这个端点来处理。其中EP0_CTRL用来对Endpoint0的传输进行控制,当CPU要向USB主机传送数据时,就会将数据写入EP0_INFIFO_DATA,EP0_INFIFO_CNT是CPU向EP0_INFIFO_DATA中写入数据的字节数。EP0_OUT,Endpoint1,Endpoint2,Endpoint3,Endpoint4的寄存器情况类似,在此不再多做介绍。UDC_STATUS和DEVICE_CTRL是接口状态和控制寄存器,对CPU和USB CORE的通信进行监控。

2.4 NandFlash

针对NandFlash读写的特点,特别是其可随机读,但无法随机写的问题,需要通过设置缓冲区来解决。在与USB Host进行数据交换的过程中,最小的单位是扇区:512字节。由于NandFlash在写之前必须先擦除,而一擦又必须擦一个Block,因此在擦除某Block之前必须保存同一个Block中有关扇区的数据。因此,如果每收到一个扇区的内容就进行一次擦、保存、写的操作,系统任务将十分繁重,无法及时响应USB Host端的请求。因此,在系统中设置32K的缓冲区,每完一次数据传输后,记下本次要写的开始扇区和总扇区数,将本次要写的数据涉及的扇区以外的数据从NandFlash中读出来,存放在缓冲区中对应位置,然后擦除一个Block,再将缓冲区中内容一次全部重新写入NandFlash。 |

|