|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

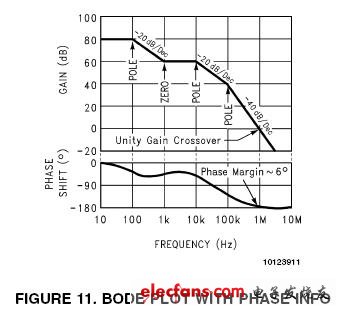

波特图分析

用包含三个极点和一个零点的波特图(图11:波特图)来分析增益和相位裕度。

图11

假设直流增益(DC gain)为80dB,第一个极点(pole)发生在100Hz处。在此频率,增益曲线的斜度变为-20dB/十倍频程。1kHz处的零点使斜度变为0dB/十倍频程,到10kHz处斜度又变成-20dB/十倍频程。在100kHz处的第三个也是最后一个极点将斜度最终变为-40dB/十倍频程。

图11中可看到单位增益点(Unity Gain Crossover,0dB)的交点频率(Crossover Frequency)是1MHz。0dB频率有时也称为回路带宽(Loop Bandwidth)。

相位偏移图表示了零、极点的不同分布对反馈信号的影响。为了产生这个图,就要根据分布的零点、极点计算相移的总和。在任意频率(f)上的极点相移,可以通过下式计算获得: 极点相移 = -arctan(f/fp) (6)

在任意频率(f)上的零点相移,可以通过下式计算获得: 零点相移 = -arctan(f/fz) (7)

此回路稳定吗?为了回答这个问题,我们根本无需复杂的计算,只需要知道0dB时的相移(此例中是1MHz)。

前两个极点和第一个零点分布使相位从-180°变到+90°,最终导致网络相位转变到-90°。最后一个极点在十倍频程中出现了0dB点。代入零点相移公式,可以计算出该极点产生了-84°的相移(在1MHz时)。加上原来的-90°相移,全部的相移是-174°(也就是说相位裕度是6°)。由此得出结论,该回路不能保持稳定,可能会引起振荡。

NPN 稳压器补偿

NPN 稳压器的导通管(见图1)的连接方式是共集电极的方式。所有共集电极电路的一个重要特性就是低输出阻抗,意味着电源范围内的极点出现在回路增益曲线的高频部分。

由于NPN稳压器没有固有的低频极点,所以它使用了一种称为主极点补偿(dominant pole compensation)的技术。方法是,在稳压器的内部集成了一个电容,该电容在环路增益的低频端添加了一个极点(图12:NPN稳压器的波特图)。

图12

NPN稳压器的主极点(Dominant Pole), 用P1点表示, 一般设置在100Hz处。100Hz处的极点将增益减小为-20dB/十倍频程直到3MHz处的第二个极点(P2)。在P2处,增益曲线的斜率又增加了-20dB/十倍频程。P2点的频率主要取决于 NPN 功率管及相关驱动电路, 因此有时也称此点为功率极点(Ppower pole)。另外,P2点在回路增益为-10dB处出现,也就表示了单位增益(0dB)频率处(1MHz)的相位偏移会很小。

为了确定稳定性,只需要计算0dB频率处的相位裕度。

第一个极点(P1)会产生-90°的相位偏移,但是第二个极点(P2)只增加了-18°的相位偏移(1MHz处)。也就是说0dB点处的相位偏移为-108°,相位裕度为72°,表明回路非常稳定。

需要两个极点才有可能使回路要达到-180°的相位偏移(不稳定点),而极点P2又处于高频,它在0dB处的相位偏移就很小了。

LDO 稳压器的补偿

LDO稳压器中的PNP导通管的接法为共射方式(common emitter)。它相对共集电极方式有更高的输出阻抗。由于负载阻抗和输出容抗的影响在低频程处会出现低频极点(low-frequency pole)。此极点,又称负载极点(load pole),用Pl表示。负载极点的频率由下式计算获得:

F(Pl) =1 / (2π × Rload × Cout) (8)

从此式可知,LDO不能通过简单的添加主极点的方式实现补偿。为什么? 先假设一个5V/50mA的LDO稳压器有下面的条件,在最大负载电流时,负载极点(Pl)出现的频率为:

Pl = 1 / (2π × Rload × Cout)=1/(2π × 100 × 10-5)=160Hz (9)

假设内部的补偿在1kHz处添加了一个极点。由于PNP功率管和驱动电路的存在,在500kHz处会出现一个功率极点(Ppwr)。

假设直流增益为80dB。在最大输出电流时的负载阻值为RL=100Ω,输出电容为Cout =10uF。

使用上述条件可以画出相应的波特图(如图13:未补偿的LDO增益波特图)。

图13

可以看出回路是不稳定的。极点PL和P1每个都会产生-90°的相移。在0dB处(此例为40kHz),相移达到了-180°为了减少负相移(阻止振荡),在回路中必须要添加一个零点。一个零点可以产生+90°的相移,它会抵消两个低频极点的部分影响。

因此,几乎所有的LDO都需要在回路中添加这个零点。该零点一般是通过输出电容的等效串联电阻(ESR)获得的。

使用 ESR 补偿 LDO

等效串联电阻(ESR)是电容的一个基本特性。可以将电容表示为电阻与电容的串联等效电路(图14:电容器的等效电路图)。

图14

输出电容的ESR在回路增益中产生一个零点,可以用来减少负相移。零点处的频率值(Fzero)与ESR和输出电容值密切相关:

Fzero = 1 / (2π × Cout × ESR) (10)

再看上一节的例子(图13),假设输出电容值Cout =10uF,输出电容的ESR = 1Ω。则零点发生在16kHz。图15的波特图显示了添加此零点如何使不稳定的系统恢复稳定。

图15

回路的带宽增加了,单位增益(0dB)的交点频率从30kHz移到了100kHz。到100kHz处该零点总共增加了+81°相移(Positive Phase Shift)。也就是减少了极点PL和P1造成的负相移(Negative Phase Shift)。 极点Ppwr处在500kHz,在100kHz处它仅增加了-11°的相移。累加所有的零、极点,0dB处的总相移为-110°。也就是有+70°的相位裕度,系统非常稳定。

这就解释了选择合适ESR值的输出电容可以产生零点来稳定LDO系统。

ESR 和稳定性

通常所有的LDO都会要求其输出电容的ESR值在某一特定范围内,以保证输出的稳定性。 LDO制造商会提供一系列由输出电容ESR和负载电流(Load Current)组成的定义稳定范围的曲线(图16:典型LDO的ESR稳定范围曲线),作为选择电容时的参考。

图16

要解释为什么有这些范围的存在,我们使用前面提到的例子来说明ESR的高低对相位裕度的影响。

高ESR

同样使用上一节提到的例子,我们假设10uF输出电容的ESR增加到20Ω。这将使零点的频率降低到800Hz(图17:高ESR引起回路振荡的波特图)。

图17

降低零点的频率会使回路的带宽增加,它的单位增益(0Db)的交点频率从100kHz 提高到2MHz。 带宽的增加意味着极点 Ppwr 会出现在带宽内(对比图15)。分析图17波特图中曲线的相位裕度,发现如果同时拿掉该零点和P1或PL中的一个极点,对曲线的形状影响很小。也就是说该回路受到-90° 相移的低频极点和发生-76° 相移的高频极点Ppwr共同影响。

尽管有 14° 的相位裕度,系统可能会稳定。但很多经验测试数据显示,当ESR >10Ω时,由于其它的高频极点的分布(在此简单模型中未表示)很可能会引入不稳定性。

低ESR

选择具有很低的ESR的输出电容,由于一些不同的原因也会产生振荡。继续沿用上一节的例子,假定10uF输出电容的ESR只有50mΩ,则零点的频率会变到320kHz(图18:低ESR引起回路振荡的波特图)。

图18

不用计算就知道系统是不稳定的。两个极点P1和PL在0dB处共产生了-180°的相移。如果要系统稳定,则零点应该在0dB点之前补偿正相移。然而,零点在320kHz处,已经在系统带宽之外了,所以无法起到补偿作用。

输出电容的选择

综上,输出电容是用来补偿LDO稳压器的,所以选择时必须谨慎。基本上所有的LDO应用中引起的振荡都是由于输出电容的ESR过高或过低。

LDO的输出电容,通常钽电容是最好的选择(除了一些专门设计使用陶瓷电容的LDO,例如:LP2985)。测试一个AVX的4.7uF钽电容可知它在25℃时ESR为1.3Ω,该值处在稳定范围的中心(图16)。

另一点非常重要,AVX电容的ESR在-40℃到+125℃温度范围内的变化小于2:1。铝电解电容在低温时的ESR会变大很多,所以不适合作LDO的输出电容。

必须注意大的陶瓷电容(≥1uF)通常会用很低的ESR(<20mΩ),这几乎会使所有的LDO稳压器产生振荡(除了LP2985)。如果使用陶瓷电容就要串联电阻以增加ESR。大的陶瓷电容的温度特性很差(通常是Z5U型),也就是说在工作范围内的温度的上升和下降会使容值成倍的变化,所以不推荐使用。

准LDO补偿

准LDO(图3)的稳定性和补偿,应考虑它兼有LDO和NPN稳压器的特性。因为准LDO稳压器利用NPN导通管,它的共集电极组合也就使它的输出极(射极)看上去有相对低的阻抗。

然而,由于NPN的基极是由高阻抗PNP电流源驱动的,所以准LDO的输出阻抗不会达到使用NPN达林顿管的NPN稳压器的输出阻抗那样低,当然它比真正的LDO的输出阻抗要低。

也就是说准LDO的功率极点的频率比NPN稳压器的低,因此准LDO也需要一些补偿以达到稳定。当然了这个功率极点的频率要比LDO的频率高很多,因此准LDO只需要很小的电容,而且对ESR的要求也不很苛刻。

例如,准LDO LM1085可以输出高达3A的负载电流,却只需10uF的输出钽电容来维持稳定性。准LDO制造商未必提供ESR范围的曲线图,所以准LDO对电容的ESR要求很宽松。

低ESR的LDO

国半(NS)的两款LCO,LP2985和LP2989,要求输出电容贴装象陶瓷电容一样超低ESR。 这种电容的ESR可以低到5~10mΩ。 然而这样小的ESR会使典型的LDO稳压器引起振荡(图18)。

为什么LP2985在如此低ESR的电容下仍能够稳定工作? 国半在IC内部放置了钽输出电容来补偿零点。这样做是为了将可稳定的ESR的上限范围下降。LP2985的ESR稳定范围是3Ω到500MΩ,因此它可以使用陶瓷电容。未在内部添加零点的典型LDO的可稳定的ESR的范围一般为100mΩ-5Ω,只适合使用钽电容并不适合使用陶瓷电容。

要弄清ESR取之范围上限下降的原因,请参考图15。上文提到,此LDO的零点已被集成在IC内部。因此外部电容产生的零点必须处在足够高的频率,这样就不能使带宽很宽。否则,高频极点会产生很大的相移从而导致振荡。

使用场效益管(FET)作为导通管LDO的优点

LDO稳压器可以使用P-FET(P沟道场效应管)作为导通管(图19:P沟道场效应管LDO内部结构框图)。为了阐述使用Pl-FET LDO 的好处,在PNP LDO(图2)中要驱动PNP功率管就需要基极电流。基极电流由地脚(ground pin)流出并反馈回反相输入电压端。因此,这些基极驱动电流并未用来驱动负载。它在LDO稳压器中耗损的功耗由下式计算:

PWR(Base Drive)=Vin × Ibase (11)

图19

需要驱动PNP管的基极电流等于负载电流除以β值(PNP管的增益)。在一些PNP LDO稳压器中β值一般为15~20(与负载电流相关)。此基极驱动电流产生的功耗可不是我们期望的(尤其是在电池供电的低功耗应用中)。P沟道场效应管(P-FET)的栅极驱动电流极小,较好地解决这个问题。

P-FET LDO稳压器的另一个优点,是通过调整场效应管(FET)的导通阻抗(ON-resistance)可以使稳压器的跌落电压更低。 对于集成的稳压器而言,在单位面积上制造的场效应功率管(FET power transistors)的导通阻抗会比双极型开关管(Bipolar ONP Devices)的导通阻抗低。这就可以在更小封装(Packages)下输出更大的电流。 |

|