1 引 言

I2C(Inter-Integrated Circuit)总线是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。是微电子通信控制领域广泛采用的一种总线标准。它是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。AT91SAM7X256是Atmel公司于2005年推出的基于ARM7的工业级芯片,他以体积小、功耗低、连接方式广泛、处理资源丰富、控制灵活等特点受到嵌入式领域开发人员的重视。本文介绍AT91SAM7X256的I2C控制器TWI接口(two-wired inte**ce)的使用方法,并以I2C设备E2PROM和日历时钟芯片为例,实现AT91SAM7X256对时间数据的读取与存储。同时,为了验证时间数据的读取与存储是否正确,使用AT91SAM7X256的在线仿真器J-LINK将E2PROM中的数据读至内存进行检查。

ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。技术具有性能高、成本低和能耗省的特点。适用于多种领域,比如嵌入控制、消费/教育类多媒体、DSP和移动式应用等。ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软件。技术具有性能高、成本低和能耗省的特点。适用于多种领域,比如嵌入控制、消费/教育类多媒体、DSP和移动式应用等。

2 硬件设计

2.1 硬件模块结构

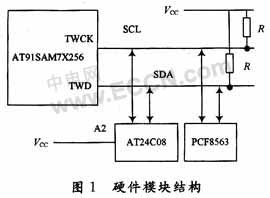

电路的硬件模块结构如图1所示。

AT91SAM7X256的TWI接口由一根时钟线TWCK和一根数据线TWD组成,产生的信号时序符合I2C总线规范;PCF8563是Philips公司推出的一款内含I2C总线接口功能的工业级时钟芯片;AT24C08是Atmel公司推出的符合I2C规约的两线串口E2PROM.AT91SAM7X256的TWCK和TWD分别与芯片PCF8563和AT24C08的SCL与SDA相连,CPU通过TWI接口将时间数据读出并存储。为了保证CPU不冲突的访问PCF8563和AT24C08,本文将AT24C08的A2管脚接高电平。由于I2C总线空闲时为高电平,所以为实现"线与"功能,总线上连接的设备均是集电极开路的,因此总线需外接上拉电阻R.AT91SAM7X256的TWI有主从2种工作模式,本文中AT91SAM7X256作为控制方,应工作于主模式。

2.2 AT91SAM7X256的TWI接口

AT91SAM7X256的TWD和TWCK管脚与设备的I/O管脚复用,同时AT91SAM7X256采用单独控制功能单元的省电方案,电源管理单元PMC控制各功能单元的时钟是否工作,所以要使用TWI接口,需要首先配置TWD和TWCK为外设连线和开路状态,其次配置PMC使TWI时钟处于工作状态。

TWI接口可提供高达400 kb/s的传输速率,为使得数据的传输速率面向不同应用,可以通过配置时钟脉冲发生器的控制寄存器TWI_CWEG调整TWCK的信号频率。

TWI接口产生的信号时序符合I2C总线规范,当读/写1个字节数据时,主设备需提供从设备的设备地址、内部地址、读写控制以及起始标志和停止标志。在数据的收发过程中,主要使用控制寄存器TWI_CR、主模式寄存器TWI_MMR、内部地址寄存器TWI_IADR、状态寄存器TWI_SR、传输保持寄存器TWI_THR和接收保持寄存器TWI_RHR.从设备地址在TWI_MMR中设置,从设备的内部地址在TWI_IADR中设置;在TWI_CR中设置是否发送起始信号和停止信号;NAK(无应答)、OVER(运行错误)、TXRDY(发送准备好)、RXRDY(接收准备好)、TX-COMP(传输完成)等状态位通过查询WI_SR得到。 写数据的过程包括:当TWI_THR写入数据后,CPU产生起始信号启动传输,TWI_THR中的数据经过并串转换后由TWD传输出去,当CPU收到从设备的应答信号后,TWI_SR的TXRDY将自动置"1",说明数据已写入从设备。读数据的过程包括:CPU发出起始信号后,若TWI_SR的RXRDY位为"1",则说明TWI_RHR中有数据等待接收,当TWI_RHR中的数据被读出后,则RXRDY自动置为"0".当读/写数据完毕后,CPU将产生一个停止信号结束传输,TWI_SR的TXCOMP将自动置"1". |