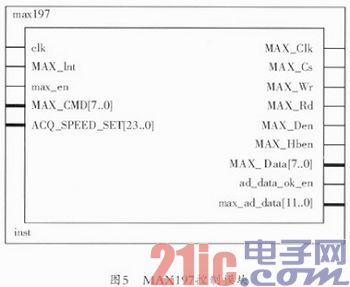

4.2 A/D转换器MAX197的控制模块设计

MAX197控制模块主要用来产生MAX197的控制信号,控制MAX197 A/D转换芯片完成模数转换,并将转换的结果存入异步FIFO,存Quartus

II9.0中用HDL语言设计生成的A/D控制模块如图5所示。

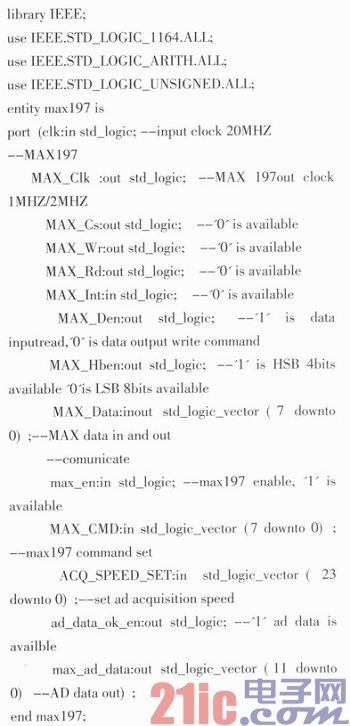

模块部分程序参考如下:

4.3 D/A转换器0832控制模块 4.3 D/A转换器0832控制模块

FPGA控制DA芯片,使DAC0832的输出与ADC芯片MAX197的输入模拟电压相加,抵消输入的零点,产生0—4.096V有效输出送到ADC芯片MAX197输入端进行模数转换,控制模块如图6所示。

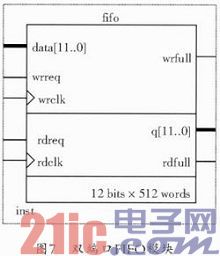

4.4 双端口异步FIFO缓存模块

由于软核处理器和FIFO的时钟不同,处理器读速度远远大于FPGA采集数据的速度,因此设计用FIFO在处理器和FPGA间的跨时钟域数据传输中起缓存的作用。在Quartus II9.0中用Altera提供的免费FIFO核设计生成的FIFO缓存模块如图7所示。

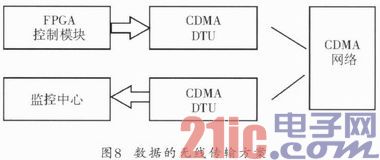

5 数据传输模块设计

数据是通过无线的方式进行数据传输如图8所示,通过CDMA网络传输,工作量小,且方便维护,成本也低,可以通过CDMA网络实现数据的实时传输。

监控中心采用查询方式接收/发送数据,数字信号处理模块采用中断方式接收数据。查询方式发送数据。在监控中心向数字信号处理模块发送数据时,先把数据发送到管理模块,管理模块再将数据发送到数字信号处理模块,当数据发送结束时,比较数字信号处理模块的模块编号和监控中心发送的模块编号是否匹配,如果匹配则接收数据并存入数据库,并实时显示,监控中心的数据显示模块主要显示监测点,以及对应的应变值、温度值和应变、温度的最大值和最小值。并将数据保存起来然后通过对数据的分析处理,对系统的结构安全状况做出评估。

6 结束语

本设计将FPGA (现场可编程门阵列)引入应力应变检测系统的设计。FPGA的时钟频率高、内部延时小、以FPGA内部的强大逻辑功能代替复杂的外围电路来控制数据采集模块组,既保证了数据采集模块实时、同步采样,又简化了硬件电路,增强了系统的抗干扰能力,具有很高的实用价值。 |