|

- UID

- 1029342

- 性别

- 男

|

在内核芯片制造前传统的验证与调试方法依赖于指令集仿真器(ISS)模型。不幸的是,ISS模型速度太慢,并且时序精度无法达到与系统硬件部分的RTL模型交互所需的要求。本文将提供一种采用虚拟系统原型实现系统级的多内核系统调试方法,该方法允许在PC机上实时执行一个完整系统的周期精确仿真,而且执行速度比基于ISS的仿真要快得多。

开发一个复杂的多内核无线系统无疑是个艰巨的挑战,特别是当内核包含有高性能处理器和先进的数字信号处理器(DSP) 时更是如此。等待硬件原型实现是不能令人接受的:关键的软硬件折衷应该在芯片制造之前尽早地完成。在内核芯片制造前传统的验证与调试方法依赖于指令集仿真 器(ISS)模型。不幸的是,ISS模型速度太慢,并且时序精度无法达到与系统硬件部分的RTL模型交互所需的要求。

在多内核环境中问题更加严重,因为单个独立的模拟器工具在调试模式下通常都缺少同步机制。结果是有些软件开发和软硬件集成工作必须等到无线硬件原型实现后才能开始。在昂贵、数量又少的硬件原型基础上进行开发和调试常常导致项目进度的延迟,并会增加芯片返工的风险。

| 图1:不同模型的速度和精度。

|

本 文将提供一种采用虚拟系统原型实现系统级的多内核系统调试方法,该方法允许在PC机上实时执行一个完整系统的周期精确仿真,而且执行速度比基于ISS的仿 真要快得多。该方法支持完整的系统级单步调试操作,其调试模式下的时序精度水平完全可以匹配实际设备指标。另外,由于虚拟系统原型能让开发人员在多系统环 境下快速精确地调试,因此给开发工作带来了极大的便利。下文讨论的包含二个ARM处理器和一个StarCore DSP的多内核无线系统实例证明了该方法的有效性。

无线SoC实例

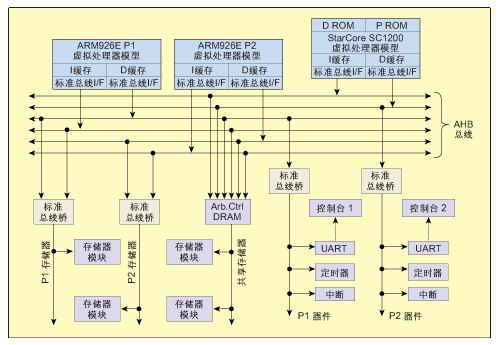

适合无线应用的一个实际多内核芯片整体架构采用了通用CPU和专用DSP内核来达到并行和专用处理的目的。另外该芯片还包含了用于片外通信的多层存储器系统和多个外围器件。

这 个特殊芯片包含2个ARM926E CPU内核,每个内核拥有独立的指令和数据缓存。其中一个ARM处理器运行Linux操作系统,并提供虚拟机、图形化环境和消息等多个普通服务。另外一个 ARM926E与DSP内核联系紧密,主要用于处理整个系统的通信和控制,需要时也能用于执行特殊任务和应用进程。拥有2个CPU可以完全实时地处理各种 业务,从而满足无线设备的各项关键要求。

作为2个ARM内核的重要补充,StarCore SC1200处理器可以加速多媒体数据处理,执行无线调制解调器的处理任务以及其它DSP任务。这块内核内置有2个独立的执行单元,每个单元都可以执行乘 法累加(MAC)以及其它信号处理算法中常用的算术操作。DSP设计用于提供大部分的语音数据处理以及MP3、MPEG-4和H.264等多媒体数据解码 服务。

作为无线芯片中的典型部件,层次化总线网络可以提供专用的数据通道,减少业务流量,并提供通信所需的公共存储模块访 问。在顶层,六条系统总线通过各自专用的存储器子系统和外围器件与处理器建立互连。所有这些总线都使用AHB协议,该协议是ARM公司定义的用于ARM处 理器内核的先进高速总线。

专用AHB总线允许全部三个处理器同时对存储器进行数据和指令存取,因而能够消除多内核设备常见的瓶颈问题。AHB系统级总线到更低层的总线通过桥进行链接。三条专用存储器总线提供对存储器模块的访问,二条低速外围器件总线连接片外通信用的定时器、中断控制器和串行接口。

当然,处理器之间也必须交换数据或控制信息。所有这类通信都是通过系统内任何地方都能访问的共享存储器完成的。利用旗语(semaphore)和邮箱(mailbox)等现成技术即可提供处理器和外围器件之间信息的安全传送。

传统的软件建模

在SoC 生产出来以后才进行验证势必会使最终产品存在大量缺陷。即使设计中嵌入了专门用于调试的访问路径,可观察性也相当有限。而在实际应用中,为了满足紧迫的产 品上市时间要求,有用的调试功能往往会被删除掉。因此协调与同步内含多处理器的硬件验证测试非常困难,为了调试故障测试在处理器之间设置交叉触发也有一定 的难度。

以前芯片架构师和设计师在芯片制造之前是利用基于软件的模型进行完整的芯片验证和调试的。最常见的方法是使用为每个处理器设计的指令集仿真器模型。这些模型执行的二进制代码与芯片中的实际处理器代码完全相同,因此这些模型可以用来在SoC制造之前开发和调试软件。

| 图2:无线SoC设计的调试要点。

|

然 而,典型的ISS模型在仿真运行大型软件(比如实时操作系统(RTOS))时速度太慢。那些具有较高性能的ISS模型在牺牲精度的条件下才能达到较快的速 度。ISS模型的主要特点仅在于精确的指令,也就是说它们能够如实地产生与制造芯片中处理器相同的结果运行代码。然而,处理器接口的逐个周期行为可能无法 匹配实际处理器内核的行为。

在开发多内核无线设备时ISS模型的缺点是一个大问题。由于对缓存和存储器的访问不具有周期精确 性,因此无法精确测量存储器性能,也无法进行详细的架构折衷。此外,针对SoC的剩余部分将ISS和硬件设计连接起来需要周期精确性,单凭指令精确性将极 大地限制可以执行的软硬件协同仿真的数量。而且不准确的时序将意味着处理器内核之间的交互操作有可能不匹配实际运行情况,从而导致芯片和硬件原型制造出来 以后还要做进一步的软件开发和反复调试。 |

|