|

- UID

- 864567

|

内部寄存器描述如表1所列。由于本系统中AD9844A工作于CCD模式,内部操作寄存器、VGA增益寄存器、箝位电压寄存器及采样增益寄存器的设置均为默认值。本设计所要做的是配置控制寄存器,选择同步时钟的极性,实现与时钟发生器的时钟同步,即采样时钟SHP/SHD为高电平触发采样周期,箝位时钟CLP为低电平有效,数据输出时钟DATACLK为下降沿触发。芯片内部寄存器的工作方式通过一个3线串口编程得到。

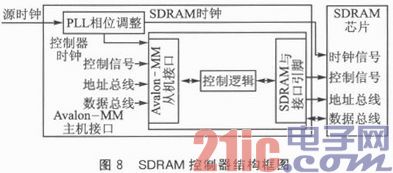

1.2.4 SDRAM模块

Avalon总线接口的SDRAM控制器结构框图如图8所示。与FPGA片内的SDRAM控制器IP核与外部的SDRAM存储器芯片之间的硬件接口,这些接口包括了SDRAM芯片的时钟接口(clk)、时钟屏蔽接口(cke)、地址总线(addr)、块选信号(ba)、片选信号(cs)、行选信号(ras)、列选信号(can)、写选通信号(we)、数据字节屏蔽信号(dqm)、数据总线(dq)。需要注意的是,PLL输出连接到SDRAM芯片和SDRAM控制器IP核模块工作的两个时钟是同频不同相的。

1.2.5 LCD显示模块

本设计采用的是一款3.5寸320×240的LQ035NC111 TFT液晶屏,此款LCD接口信号归为5类:

①数字信号接口,如RESET、SPENA、SPCLK、SPDAT、Rx、Gx、Bx、HSYNC、VSYNC、DCLK和DE。此类接口主要是传输显示数据给LCD面板。

②液晶的模式设置专用输入接口,包括IF0、IF1、IF2等信号,它们的主要功能就是设置数据传输模式,本设计采用RGB数据传输。

③触摸屏信号接口,是模拟信号,如Y1、X1、Y2、X2。

④电源接口。

⑤背光电源,即VBL+和VBL-。

图9中各个模块设计好后,打开SOPC,添加Nios II处理器、片内存储器、系统ID和LCD显示组件,分配好地址和中断优先级后,然后生成系统。把生成的系统和上面各模块例化到顶层模块中,分配好引脚,做好时序约束,编译整个工程,完成硬件部分的设计。其中顶层模块包括:

◆sys_ctrl模块:系统复位信号和PLL控制模块。

◆tcd1501d模块:CCD系统模块。

◆ad9844a模块:A/D控制模块。

◆sdram模块:SDRAM封装控制模块。

◆sdfifo模块:读/写SDRAM数据缓存FIFO模块。

◆LCD模块:LCD显示模块。

2 系统软件程序

软件程序主要是数据处理和LCD的显示。数据过来后先清屏LCD,接下来就是坐标的一些定位与溢出处理,以满足从左到右、从上到下的显示顺序。

(1)LGD写数据函数

void lcd_wrdb(alt_u16 xaddr,alt_u16 yaddr,alt_u16 cor);

其中xaddr、yaddr、cor分别为X坐标地址、Y坐标地址和显示的色彩。

(2)显示函数

void print_db(alt_u16 row,alt_u16 col,alt_u8 *ptr,alt_u16 cor_b0,alt_u16 cor_q0);

该函数功能为在指定的位置显示数据。

部分主函数程序如下:

结语

本文在Nios II处理器的基础上实现了CCD采集系统的设计,经测试,该方法能较好地采集光电信号,并把图像实时地显示到LCD上,达到了本设计的预期目标。该方案稳定可行,程序操作性强,在图像采集和处理上具有一定的参考价值。 |

|