|

- UID

- 1023229

- 来自

- 中国

|

3.4 子密钥延迟控制

图3中的子密钥延迟控制单元可完成子密钥的延迟控制,它由一系列寄存器构成。通过时钟触发数据块依次向下传输给各级流水线,子密钥依次存入下一级寄存器,在相应数据块加密时从寄存器读取,便实现16个不同数据块同时加密。在新更换密钥时,各个子密钥分别存入寄存器(i,1),随时钟触发依次在流水线寄存器中流动,以前在流水线上继续使用的子密钥也同时在流水线寄存器中随数据块流动,通过合理使用寄存器,完成数据块和子密钥的同步,准确快速分发子密钥,实现密钥的动态更换。

4 仿真结果

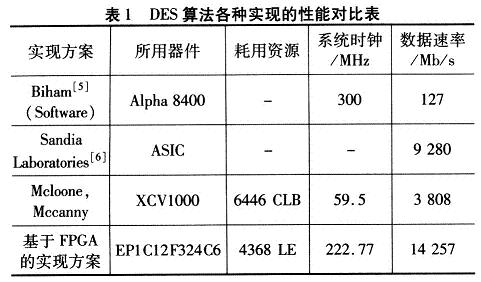

采用VHDL作为设计逻辑描述.以OuartusⅡ作为设计开发工具,以Ahera公司Cyclone EPlCl2F324C6为目标器件,逻辑综合结果表明系统共占用4 368个逻辑单元(LE),系统的最高时钟频率为222.77 MHz,对信息的加密速度为222.77x64 Mb/s=14.26 Gb/s。由表1给出的DES算法有关硬件和软件实现性能对比结果表明,该系统的数据加密速度是最快的,是软件实现的112倍.同时其资源消耗指标也较理想。

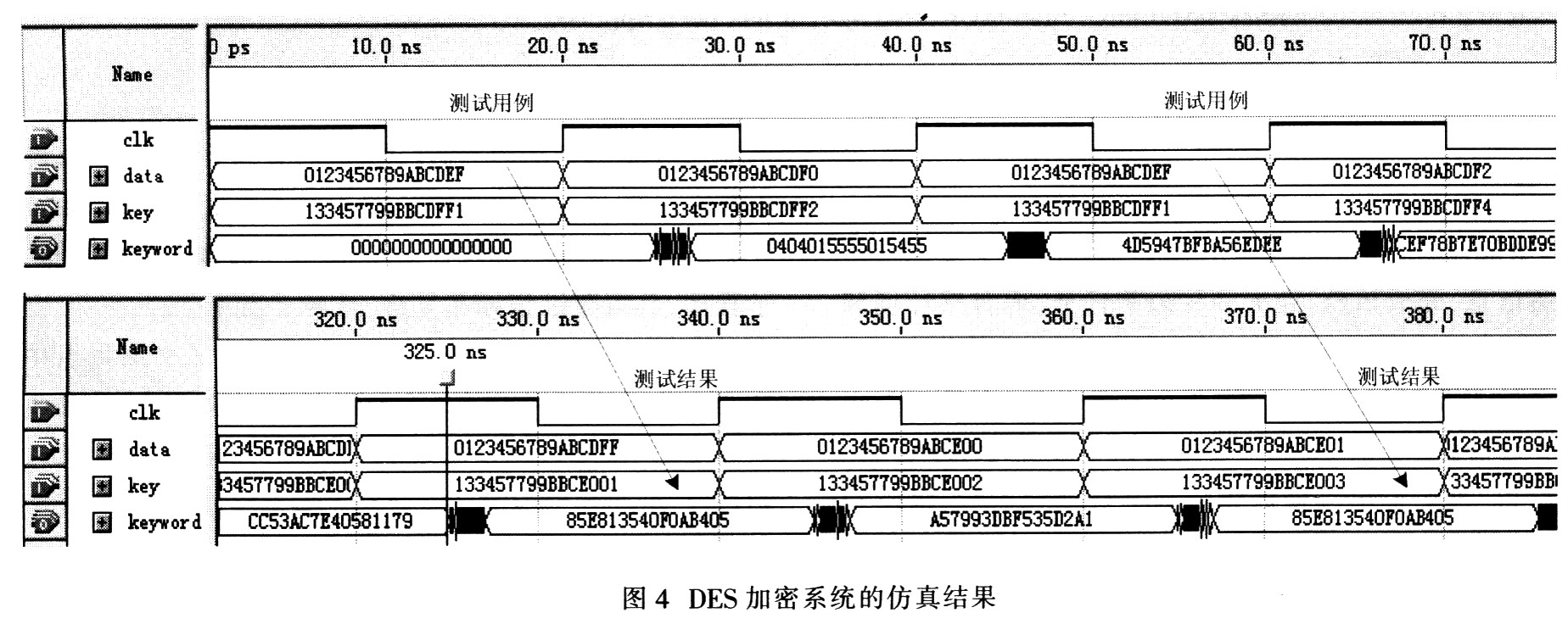

假设需要加密的明文M=0123456789ABCDEF H,密钥K=133457799BBCDFFl H,经过初始置换,16轮迭代加密,逆初始置换,最终的加密密文应为:85E813540FOA8405H,其时序仿真结果如图4所示,仿真结果表明,系统完全实现DES算法的流水加密功能。

5 结语

在分析DES算法原理的基础上,详细阐述了一个基于VHDL描述、FPGA实现的DES加密算法系统的设计和仿真结果。该系统与传统软件加密系统相比,设计灵活,处理速度快,密钥可动态刷新,抗解密强度高,稳定性好,重用性强,升级方便。 |

|