|

- UID

- 864567

|

随着信息技术的发展,对信号的测量技术要求越来越高,示波器的使用越来越广泛。模拟示波器使用前需要进行校正,使用比较麻烦;而数字示波器,由于受核心控制芯片的影响,对输入信号的频率有严格的限制。基于FPGA的数字示波器,其核心芯片可达到50万门,配合高速外围电路,可以测量频率为1 MHz的信号,有效地克服了以往示波器的不足。 1 系统方案设计

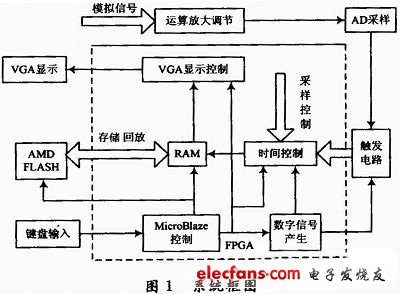

设计的数字示波器系统主要使用了Xilinx系统的开发环境,并在此环境内部建立了AD采样控制模块、键盘控制模块、VGA显示模块等多个模块,从很大程度上减少了硬件电路的搭建,也因此提高了系统的稳定性和可靠性,系统框图如图1所示。

另外,设计使用XPS将32位的MicroBlaze微处理器嵌入到了FPGA中,实现了可编程片的嵌入以及在可编程片上的系统设计。MieroBlaze通过LBM总线访问片上的存储模块BlockRAM,然后通过OPB总线上挂接外设进行接口连接和驱动。

VGA显示部分采用双缓冲机制进行工作,在FPGA内部建立RAM,按照一定时序降RAM内的缓存数据映射到VGA显示屏上。

2 硬件设计

2.1 信号调理电路模块

信号调理电路模块,对输入的模拟信号进行处理,由于输入电压幅度为-2.5~+2.5 V之间,而后一级的AD模块采用了12位的高速A/D转换芯片ADS804,只能对0~2 V的电压进行模/数转换,故需要将输入电压先抬升为0~5 V,在应用运算放大器进行比例缩小,达到0~2 V的模数转换要求。

2.2 A/D转换电路

A/D转换模块采用存储采样数据的并行数据处理方法,这样可以使硬件电路得到最大程度的简化,同时也提高了系统的稳定性。AD部分的采样,选用实时采样技术。能够捕获到单个信号。采样速率为10 MHz,即在最高频率1 MHz时,实时采样可以在每周期采10个点以保证取到一个完整的信号波形。

2.3 触发电路模块

触发电路模块属于外触发,对模拟信号实现任意电平触发,该模块采用电压比较器来实现单次触发。

2.4 存储模块

存储模块包括内存储和外存储两部分,使用外部电路进行搭建的为外存储,内存储在软件部分进行说明。

外部非易失性存储器模块采用存储容量为16 KB的E2PROM芯片24C128,该芯片作为手动存储的存储介质,从而实现掉电不丢失的设计目的。 |

|