摘要:在级数的基础上,设计一种基于FPGA的多项式运算器。利用该运算器可以在数字系统设计中更好地处理和应用各种函数。首先实现基于FPGA的多项式运算器,利用这个基本单元,进而实现了比较复杂的函数。经过验证,该运算器结构简单,运算实时性和准确性都能很好地满足需要,最后对数据进行了误差分析。

关键词:多项式;运算器;FPGA;电路设计

0 引言

传统的DSP都基于CPU结构,是一种基于特定指令系统的处理器,但随着运算时钟越来越接近电子器件可以接受的极限,这种DSP的处理能力也在接近它的极限;另一方面随着EDA技术的发展,尤其像FPGA和CPLD器件的成熟和应用,可以通过直接设计电路来实现并行的运算,这样运算的效率从本质上得到了提高,而且目前能实时地实现非常复杂的运算,所以基于FPGA的运算器被提上议事日程,并受到越来越多的重视。一种便于用电路实现而且通用性强的算法,可以帮助工程师简单高效地完成一个能在FPGA上工作的运算器的设计。

1 数字电路实现运算的优缺点

初步的FPGA设计是用硬件描述语言完成器件逻辑功能的描述,一个好的设计必须考虑数字电路的特点。CPU是一个典型的数字电路,因为其只能做加法运算,所以需要通过程序将各种运算都转换为加法来完成。传统的“数值分析”正是在这种程序设计的基础上形成的,不但复杂而且效率不高,不能实现真正的实时运算,而FPGA本身除了能做加法运算外,做无符号数的减法和乘法也很方便。目前两大FPGA生产商推出的集成开发软件中,都有集成的加、减法和乘法的IP核,运算效率非常高,对于无符号数的运算一般只要1个时钟,甚至是不需要时钟的组合逻辑电路,文献中也有这些运算器的详细介绍。但是直接做除法则不同,虽然也有除法IP核,但是需要许多个时钟,而且占用逻辑资源很多,无论设计还是应用都不方便。电路运算的另一个缺点是表示有符号数和小数,以及做有符号小数间的运算也很麻烦。所以在设计DSP时总是希望能够找到一种方法尽量的趋易避难。

2 麦克劳林级数和多项式

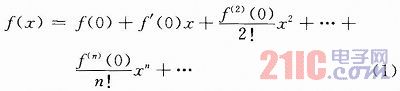

运算器的作用是对数据进行各种运算,这个过程可以用一个函数来表示:y=f(x)。任何一个在零附近连续的函数都可以展开为麦克劳林级数:

大部分常用函数的高阶导数项很小或者为零,所以在精度允许的范围内取其中的有限项就可以,即用一个多项式做近似运算,多项式运算的特点在文献中有详细介绍。用FPGA实现多项式的运算,处理很多复杂的函数将会十分方便。

y=a0+a1×x+a2×x2+…+an×xn (2)

本文讨论的是一种可以用FPGA或CPLD实现多项式(2)运算的运算器。对于简单的多项式可以是一个组合逻辑电路,不需要时钟,所以运算效率很高。这样许多运算都可以简单而且高效的完成。3 运算器设计

3.1 四则运算电路

文献中瞄述了各种无符号整数间的运算电路。虽然也可以进行用反码表示的符号数的运算,但不倾向于使用。因为需要做四则混合运算;反码易于做加、减法,但不易做乘、除法。而用非反码的带符号位的数据,符号位做单独计算,其余数据做无符号运算,整个计算结构是最简单的。另外即便是无符号数做除法也很复杂,不过考虑到有种特殊的除法运算除外,那就是对于二进制数去掉最末位就相当于除以2。所以运算时可以尽量避免除以非2倍数的数,以此来简化计算。

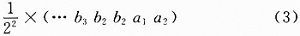

表示小数在计算中是必须的。文献中介绍了二进制定点小数,比如需要保留数的2位二进制小数位,可以将二进制小数“…b3b2b1.a1 a2”表示为:

运算中还是可以视为对整数的计算。这样用无符号的定点数进行计算,配合独立的符号位表示正负,就可以用简单的无符号运算器进行复杂的运算。

3.2 多项式的变换

式(4)为一个3次多项式,以它为例来介绍设计方法:

y=a0+a1×x+a2×x2+a3×x3 (4)

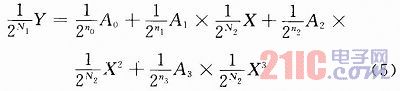

首先将式(4)中所有的数都用一个符号位加无符号二进制形式表示。分别用N1,N2表示y和x中包含的小数位数,可以将式(4)写成:

式中:X,Y是x,y去掉小数点后的整数(注:这里和式(3)一样只是去掉小数点,不是去掉小数位)。A0,A1,A2,A3作为系统的常数也是一样;n0,n1,n2,n3分别是a0,a1,a2,a3二进制形式的小数位数。可以进一步变换式(5)为:

不难发现式(6)是很容易实现的。先进行各项符号位的计算,然后就只剩下无符号整形数据计算;而且除法全是除以2的倍数。最后各项之间根据符号位做加、减运算就得到输出Y,是带符号有N1位小数的定点数。3.3 设计实例

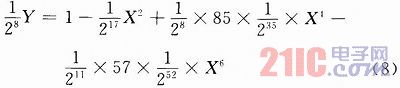

以设计余弦函数为例,用6次多项式可以很好地拟合(0,π/2)上的余弦函数。先用麦克劳林级数计算得到6次拟合多项式:

考虑到三角函数只有小数部分有效,所以数据只用1个整数位、另8个小数位和一个符号位表示。另外需要说明的是常数保留的小数位是可以调节的,选择保留合适的常数小数位可以尽量在保证精确度的情况下简化运算。

确定数据格式后式(7)可以写成式(8)的形式,进一步可将式(8)变化为式(9),并在XILINX公司的ISE中完成设计。

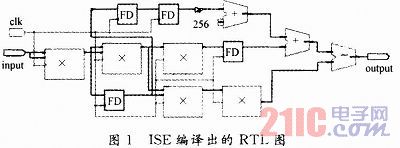

设计中考虑到纯粹的异步组合逻辑电路容易出现“竞争-冒险”,所以加入了同步时钟,这里利用同步时钟分三步完成运算,同时为了使每一步的运算保持同步还需要加入延时模块,这样虽然牺牲了一些时间,但是保证了运行的稳定性。图1是将多项式(9)用ISE编译出的RTL电路图,其中“input”为式(9)中的X,“×”为乘法器,“FD”为延时模块,“output”为式(9)中的Y。

将设计下载到芯片XC2VP30,并用Chipscope进行片内逻辑分析,外部时钟和采样时钟都是100 MHz,得到电路的输入/输出曲线(见图2)。图2中虚线是输入变量x,实线是输出变量y。纵坐标的数值显示的是Y=y×28的值,即显示时没有考虑小数点。

从图2中可以看到,输出有大约3~4个时钟的延时,对比CPU执行1条指令就需要3~4个时钟,运算效率已经很高,而且这里使用的逻辑资源很少。

4 实验结果分析

多项式拟合函数会有误差。这里只分析运算器相对多项式的误差。因为数据位宽有限,会出现截断误差。设计实例采用8位小数位,最大表示误差是±2-9。由于常数也有数据截断,实际运算误差会更大。

减小误差的惟一办法是增加数据的位数。在本例中将数据上传电脑并测算,最大误差在x=π/2处,绝对值是0.0063,相对值是0.63%。对于一些特殊的输入如x=0或x=0.5等,运算没有误差。

5 结语

通信系统的仿真与硬件实现涉及到很多复杂的函数,直接实现会造成资源浪费,而且实现难度比较大。采用FPGA实现多项式运算,实现起来比较简单,为之后实现复杂函数提供了基础,大大提高了运算速度和实现效率,在通信系统的硬件实现上有很广阔的应用前景。 |