ADC技术在SDR实现中的挑战 更新于2012-07-24 04:25:53 文章出处:互联网

ADC SDR 挑战

本文主要讨论模拟数字转换在SDR实现中的挑战,以及ADC的哪些突破可以促进软件无线电的实际应用。

存在的问题

SDR对于电信公司来说,可以以最少的基础设施部署成本,满足覆盖范围宽广的无线电频率与标准,并应付它们的未来演进。针对此需求,要求设计具有足够的弹性,以支持比平常更宽的频带,并提供超过窄频应用所需的动态范围。即最终必须能够在多载波环境中,处理调制方式与带宽皆不同的载波,以及信号阻隔(blocking)等需求。

DSP技术的进步已大幅提高无线射频系统数字后端的功能,有助于SDR的实现。目前还缺少的,就是将敏感度极高的模拟信号转换为处理方便的数字信号。在这些无线电系统中AD转换对于实现最终的目标非常重要。无线射频系统的接收器(Rx)和发射器(Tx)都会用到ADC,它是SDR应用中不可或缺的器件。

ADC重要规格

灵敏度与可用带宽是无线射频系统接收器设计的主要规格。灵敏度是指无线射频系统对天线输入端微弱信号的处理能力,通常以dBm表示。对ADC而言,灵敏度通常转换成信噪比(SNR)指标,并以dBc或dBFS表示(dBc是以载波信号为基准所表示的信噪比,dBFS则是以ADC的满刻度输入为基准)。无线射频系统的小信号接收能力以及大干扰信号抑制能力皆与ADC的无杂散动态范围(SFDR)密切相关,SFDR是目标信号(载波)与ADC输出中次高的杂散信号(无论是否为谐波)的比值,通常以dBc表示。

最后,转换器的可用带宽其实是定义不明确的名词,主要指ADC在适当SNR和SFDR性能下所能处理的实际信号带宽。在业界标准做法里,ADC规格是以模拟输入频率响应的-3dB为参考点。然而,现今许多转换器虽标示有高达数百MHz的带宽,实际性能却在模拟输入频率增加到200-300MHz后就大幅下降。

带宽考虑

SDR的重要优点之一,是它不需要新硬件就能处理更大频率范围,就当前的全球频谱使用情形来看,此点格外吸引人。每一种无线技术标准都会定义多种工作频率,例如,GSM就能在400MHz、850MHz、900MHz、1800MHz、1900MHz甚至2500-2690MHz的GSM延伸频带上工作;3GPP频率包括1800MHz、1900MHz和2100MHz;WiMAX频率则包括2500MHz、3500MHz和往上一直到5GHz,而且未来还会应用在更多的频率上。

由于频率种类复杂繁多,通过ADC尽可能把最大信号带宽数字化就成为一项重要优势,这也使得ADC的采样频率成为这类设计的重要关键。根据奈奎斯特条件,ADC在不产生迭频(aliasing,目标信号数字化后混迭自身而造成失真的过程)下所能数字化的带宽,为其采样频率一半 (Fs/2)。例如,采样频率为200MSPS的ADC最大能将100MHz带宽的信号数字化。然而在实际应用里,负责将模拟输入端带宽限制为Fs/2的滤波器不可能是完美的,因此会降低实际可用的带宽。

除了接收器外,大带宽对无线发射来说也很重要。由于功率放大器成本与其输出功率成正比,提高效率就成为减少零件用料和工作成本的重要方法。现代的数字预失真算法虽能将发射器功率放大器线性化,却需要将带宽放大到发射信号带宽的好几倍,再将此数字化带宽回授给数字处理器,因此采样速率极高的ADC在系统中即为一不可或缺的角色。

信噪比

为了维持最高灵敏度,SDR必须拥有很高的信噪比,以分辨微弱信号和进行解调。无线技术标准演进到6?QAM等高阶调制机制后,对于ADC的信噪比性能要求更为严格。当天线接收输入功率很低时,ADC的信噪比(再加上本地振荡器的相位噪声)就成为限制因素,决定整个接收器的灵敏度。

SDR设计人员直到最近都还必须牺牲信噪比来提高采样频率(带宽),因为采样率高达数百MSPS的最先进ADC只有10位,信噪比则在50dBFS左右。随着ADS5463(12位/500MSPS)的出现, ADC的采样频率已大幅提高一倍(过去最高仅250MSPS),使信噪比跃增至65dBFS左右,可以实现过去无法做到的许多设计。

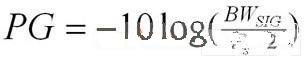

除了能够有效重建最大模拟信号带宽外,处理增益是ADC采样频率的另一项附带优点。一般而言,ADC的信噪比都是以正弦波功率与转换器在整个奈奎斯特频带(从0Hz到Fs/2,不包含直流)噪声总和的比值来计算,总噪声通常会均匀分布在奈奎斯特区域。当接收器处理该区域的某个频带信号时,数字滤波器就能大幅衰减该频带以外的噪声。假设目标信号带宽为BWSIG,ADC的采样频率为Fs,则实际的处理增益可计算如下:

图1是采样速率为500MSPS ADS5463这类超高速ADC所能提供的处理增益。SDR的数字后端可以充分利用ADC的宽带性能优点。

图1:ADC在500MSPS采样频率下的处理增益与目标信号带宽关系图。

无线接收器不断进步,最后将能直接采样射频信号。这类作业所需的ADC技术虽未出现,但相关技术突破是可预期的。值得注意的是,信号抖动最后也会对信噪比造成限制,也要列入考虑。在采样系统里,下列公式2表示信噪比与抖动之间的关系:

其中fin代表模拟输入频率,tjitter则是系统抖动的均方根值。ADC采样电路的内部抖动会以平方根和的方式,加到外部提供的转换器采样时钟。值得注意的是,信噪比的限制与实际采样频率无关,但会直接受到模拟输入频率的影响。这项基本限制将影响决定接收器中频位置时,亦即当中频提高时,简化接收器架构和滤波电路(也就是降低成本)的好处,会被ADC频率和抖动造成的限制所抵消。

无杂散信号动态范围

ADC的线性特性通常以其无杂散信号动态范围(SFDR)表示,在接收器天线的入射功率达到相当水平时,此特性变得非常关键,这可能发生在当目标信号很强(理想情形),或频带内出现强干扰之时。如果是后者,ADC的线性特性就决定了目标信号能否被解调,特别是当目标信号功率很低时。由于强干扰的出现,可能会让总信号(目标信号加干扰源)接近模拟输入的满刻度范围,而限制了任何自动增益控制(AGC)功能的应用。此时,ADC固有的线性性能就变成了瓶颈。

就像抖动会限制SDR设计师可以设定多高的中频一样,SFDR对其选择也有很大的影响。市场虽有许多ADC具备良好的线性特性,但都仅限于输入频率在200MHz以下,使高中频的优点受到SFDR滚降性能限制而无法实现。

采用最先进BiCMOS工艺技术的新型模拟架构实现了模拟输入缓冲器的集成,可在高达数百MHz的范围提供很高的SFDR性能。ADS5463的模拟输入缓冲器能将敏感的模拟输入与转换器内部的开关电路完全隔离开,使设计师能轻易达到器件数据手册所列的性能。另外,ADS5463能在输入频率范围提供固定不变的阻抗值。ADS5463至少能在500MHz中频范围达到超过70dBc的SFDR性能。激增的性能将大幅简化无线电设计,当它配合非常高的信噪比和处理增益时更为有用。采用超高输入频率能进一步降低无线电成本,能省下额外的降频转换步骤与相关的元件材料。

本文小结

最新的混合信号技术,已能在前所未见的采样频率和模拟输入频率上提供强大性能,不但简化无线电设计,并提供更大工作带宽及更高灵敏度。ADC技术不断突破极限将持续为真正可重配置多标准无线电的来临奠定基础 |