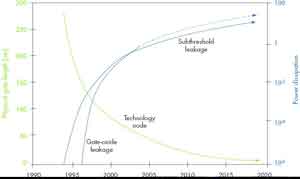

电子发烧友网核心提示:随着工艺尺寸的减小,数字逻辑电路的漏电流成为当前FPGA面临的主要挑战。静态功耗增大的主要原因是各种漏电流源的增加。图1所示为随着更小逻辑门长度的技术实现,这些漏电流源是怎样随之增加的。此外,如果不采取专门的功耗措施,较大的逻辑电容和较高的开关频率也会导致动态功耗增大。

功耗由静态和动态功耗组成。静态功耗是采用可编程目标文件(.pof)对FPGA进行设置,但时钟还没有工作时消耗的功率。数字和模拟逻辑都存在静态功耗。在模拟系统中,静态功耗主要来自模拟电路不同接口配置带来的静态电流。

图1 在更小的工艺尺寸上,静态功耗显著增大

动态功耗是器件工作时由于信号触发和容性负载充放电所带来的功耗,影响动态功耗的主要因素是电容充电、供电电压和时钟频率等。按照摩尔定律,小工艺尺寸降低了电容和电压,从而降低了动态功耗。而难点在于小工艺尺寸上实现了更多的电路,提高了最大时钟频率。随着工艺节点的减小,相同电路的功耗在降低,但是FPGA容量在不断加倍,最大时钟频率不断提高。

体系结构和工艺技术的功耗创新

FPGA可以采用创新的内核、I/O和收发器体系结构以及最新的工艺技术和电路技术来解决这些功耗难题。

1 可编程功耗技术

FPGA内核主要包括逻辑、存储器和数字信号处理(DSP)模块。在Virtex-5 FPGA等标准FPGA中,所有逻辑模块都设计运行在一个速率上——最大速率,导致非常大的功耗。

Altera公司的工程师分析了71个设计的基准测试结果,估算一个设计一般需要多少高速逻辑。他们对设计进行编译,在FPGA架构上实现所能达到的最佳性能。在这些设计中,所需要的高速逻辑大概平均占20%。

图2所示为一个典型的余度直方图,大部分通路(左侧)都有一定的余度,只有少量关键通路(右侧)需要性能最好的逻辑以达到时序要求。

图2 余度直方图显示少量电路没有或者很少有余度

利用这一事实——设计中的大部分电路都有一定的余度,不需要将所有逻辑置于高性能状态。以Stratix IV FPGA为例,它由逻辑阵列模块(LAB)、TriMatrix存储器和DSP模块构成,利用可编程功耗技术将少量的关键时序逻辑模块设置为高速模式。时序不重要的逻辑模块设置为低功耗模式,能够大大降低低功耗逻辑的泄漏功耗。而且,可编程功耗技术将没有使用的逻辑、TriMatrix存储器以及DSP模块设置为低功耗模式,进一步降低了功耗。

在任何设计中,Quartus II软件能够自动确定设计中每一通路的余量,通过调整晶体管反向偏置电压,把晶体管,同时把逻辑模块设置为合适的模式——高性能或者低功耗。例如,将Stratix IV FPGA内核的n-MOS晶体管设置为这两种模式。

● 低功耗模式,Quartus II软件减小反向偏置电压,使得晶体管很难接通。这降低了时序不重要电路的亚阈值漏电流和不需要的静态功耗。

● 高性能模式,Quartus II软件增大反向偏置电压,在几个关键时序通路上的晶体管更容易接通,以满足设计中规定的时序约束要求,提高性能。

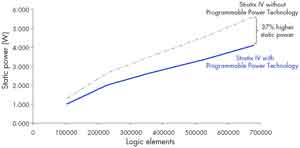

采用同样的方法也能将p-MOS晶体管设置为合适的模式,从而设置LAB、TriMatrix存储器和DSP模块为高性能或者低功耗模式。这样,通过改变晶体管的电气特性,Stratix IV FPGA可编程功耗技术以高速逻辑和低功耗逻辑的最佳组合,实现了最好的性能和最低的功耗。例如,图3所示的Stratix IV EP4SE680 FPGA在85℃时的典型设计,和没有采用可编程功耗技术时相比,静态功耗降低了37%。

图3 可编程功耗技术降低了静态功耗

我们可以精确地控制一个设计达到其性能要求而需要的高速逻辑数量。在每一个逻辑块基础上控制高速和低功耗逻辑的设置(每个逻辑块包括两个LAB,或者一个LAB和DSP模块,或者一个TriMatrix存储器,都含有相关的走线)。例如,在Stratix IV FPGA中,可以分别对5000多个逻辑块进行控制,设置为高速或者低功耗模式,把设计功耗降到最低。Quartus II开发软件能够将逻辑块设置为高速或者低功耗模式,自动对设计进行优化,无须用户的干预。

Quartus II软件每次针对Stratix III FPGA进行设计编译时,自动对设计进行优化,达到规定的时序约束,同时实现最低功耗。得到的编程文件被装入FPGA,包括将每个逻辑块设置为高速或者低功耗配置的信息。在Quartus II软件中完全可以看到逻辑块高速或者低功耗模式的最终设置。 |