|

- UID

- 863084

|

电子发烧友网核心提示:如今,大多数通讯系统均将FPGA作为其产品解决方案,且已有大量FPGA应用到通讯系统之中。为了达到降低系统维护的成本的目的,我们就需要实现FPGA远程更新重启系统的功能。本文将以Xilinx VIRTEX-6 FPGA开发板为例,给大家介绍FPGA远程更新重启系统的整个配置过程。

FPGA加载主要分为2大类,一类是主动模式(master)另一类是从模式(slave)。在主动模式时FPGA会外挂存储器存储FPGA bit映像,FPGA 会主动提供时钟访问外部存储器。在从模式时,FPGA作为从设备被挂在控制器CPU上由处理器控制对FPGA编程。上述两种模式中,因为从模式FPGA由外部CPU控制编程,可以通过远程更新CPU文件就可以实现对FPGA的版本更新,非常方便。但是当CPU外挂的FPGA较多时会使系统加载时间过长,降低系统启动速度。这里将利用FPGA 多重启(multi-boot)功能实现在主动模式下版本更新。

远程更新流程

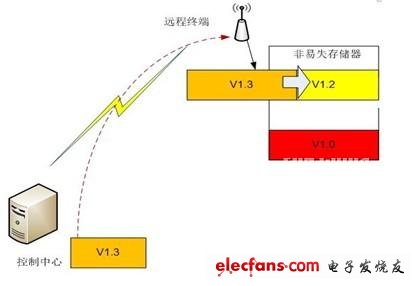

当系统需要升级时,中心控制系统需要将新的FPGA比特映像文件直接发布到远程子系统,由远程 子系统将比特文件更新到非易失存储器。然后由FPGA内部控制逻辑重新启动。比特映像文件更新后,下次上电启动将从新的比特映像文件。如图 1FPGA远程更新系统

图 1 FPGA远程更新系统

多重启动 FPGA 介绍

a)多重启动介绍

VIRTEX6可以支持2套配置文件,第一个版本为安全版本存放在起始位置(spi起始地址为0),第二个版本为最终启动版本。当FPGA启动时,加载控制器会从地址0开始读取加载指令。当读到WBSTAR和IPROG指令时,控制器就跳转到WBSTAR指定的地址读取新的加载指令。在第二个配置文件中不再发IPROG指令,控制其将顺序执行以直到配置文件结束。配置顺序如图 2。

图2 多配置文件加速过程 |

|