|

- UID

- 864567

|

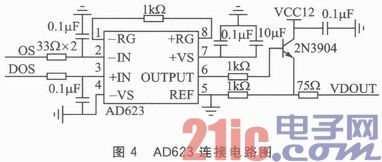

1.2.2 AD623模块

AD623集成了3路运放,可单电源或双电源工作,具有较高的CMRR和极低的电压漂移。除了一个可编程的外接电阻外,所有元件都集成在内部,提高了电路温度稳定性和可靠性。AD623的连接电路图如图4所示,将视频信号及其补偿输出分别送至AD623的反相和同相输入端,在AD623的输出端接一级射极跟随器以增强信号的驱动能力。选用该器件可消除采用普通运放和外围电阻所引起的输出信号的温度漂移。

1.2.3 AD9844A模块

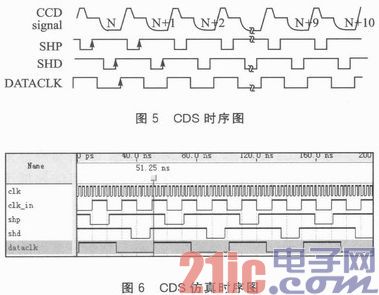

AD9844A是ADI公司的一款面向CCD的完善的低功率单通道模拟信号处理器,具有采样速率高达20 Msps的单通道输入体系结构,这种设计能采样并处理隔行扫描CCD阵列后所得的输出信号。芯片要求的时序图如图5所示,图6为仿真得到的时序图。

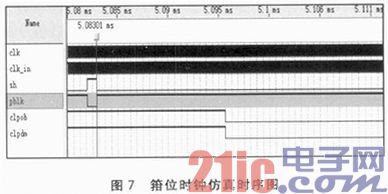

AD9844A是集相关双采样、自动增益放大、12位A/D转换于一体的可编程集成芯片,可配置为CCD-Mode、AUX1-Mode等多种模式。其中AUX 1-Mode对交流耦合信号进行采样,没有相关双采样;CCD-Mode可对CCD输出进行CDS处理。CCD帧信号的箝位时序,包括PBLK、CLPOB、CLPDM。其中线性输入箝位电路(CLPDM)用来消除CCD视频信号暗像素电流偏置,要求CLPDM脉冲覆盖整个CCD的48个暗像素;预消除电路(PBLK)用于水平箝位,削弱帧水平转移时所带来的暗电流噪声,要求与sh同时有效;光学暗点箝位电路(CLPOB)用于调整A/D转换后的视频变化和剩余偏差。这3个时序有非常严格的要求,这也是相关双采样箝位电路难于实现的原因。图7是箝位时钟仿真时序图。

|

|