|

- UID

- 864567

|

(1)算法移植:一般算法的编写都会在Matlab上实现,虽然它是一种类C语言,但和标准的C相比还是有着很多的差异,而且Matlab中往往提供了各种信号处理的工具箱,如图像处理、神经网络、小波变换等等。我们只要简单的调用这些函数来,带入几个参数即可以方便的进行各种信号处理。所以,当把这些算法移植到本系统的DSP中时,一些函数还得重新编写,还有编程格式、风格都要有所更改,有些地方为了提高算法的效率,充分利用DSP的资源,还应该把部分代码编写成汇编语言等等。当把整个算法都移植完后,最后封装成一个函数,这样更易于整个算法的维护及调用。然后,当触发条件满足时,用DSP/BIOS中的某个任务来调用这个算法处理函数来完成对车牌图像的识别。

(2)底层驱动的开发:底层驱动的编写采用CCS自带的CSL(Chip Support Library)来进行底层驱动开发,CSL提供一系列应用程序接口(API,Application Programming Interface)用于配置和控制DSP片上外设,从而简化了DSP片上外设的开发工作,大大缩短了开发周期。

2.3 FPGA功能模块

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。FPGA的使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能。FPGA在通信、数据处理、网络、军事和航空航天等众多领域得到了广泛应用。

本系统设计中,FPGA作为图像采集、存储以及传输的核心模块,协调及控制着整个系统的正常运行,起着非常重要的作用。本系统选用了Altera公司性价比较高的Cyclone系列中的EP1C12Q240型号FPGA。该FPGA共有52个存储块,共239616bits。通过QUARTUS II自带的MegaWizard工具可以将每个块配置成不同的存储模式,如单口RAM、简单双口RAM、移位寄存器、ROM和FIFO等,这样有利于本系统在采集图像时暂存图像数据及把FPGA作为SBSRAM供DSP访问的设计。该FPGA有着片上足够多的IO口也为本系统以后扩展留下了空间。

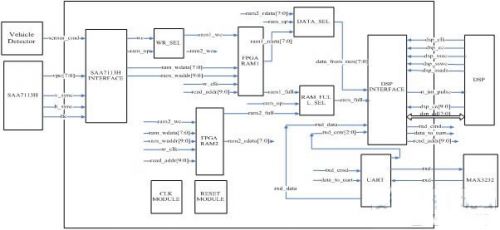

这里与FPGA相连的器件有:SAA7113H、SDRAM、DSP以及MAX3232。由于FPGA纯粹是一个编程器件,其IO脚可以配置成任何我们需要的信号,与任何接口可以相接,所以硬件接口设计上比较简单。难点在于编写各种通信协议和不同的接口进行无缝传输。整个FPGA的程序设计总体框图5所示:方框内的部分为FPGA的各个模块以及它们之间的相互连接。方框以外的部分是FPGA的外围器件。

图5 FPGA的程序设计总体框图

该FPGA系统在整个车牌识别系统中起到图像的采集、缓存和传输的功能。当车辆检测器的感应信号sensor_cmd信号有效时,启动SAA7113H_INTERFACE模块内部的状态机进行图像的采集工作,SAA7113H_INTERFACE模块从SAA7113H的视频流中检测到场开始信号时,开始一帧图像数据的传输。由于视频流为PAL制,所以一帧图像分为奇场和偶场两场图像数据。

系统采用了乒乓结构的设计方法,这种典型的设计方法在“以面积换速率”的FPGA设计方法中经常得到应用。于EP1C12Q240C8内部共有52个存储块,共239616bits,所以在FPGA内部设计一个小存储量的RAM是可行的。系统中设计了两块720*8bits(每行图像数据大小)的空间,这两个存储器的写时钟信号是SAA7113H输出时钟LLC的2倍。SAA7113H INTERFACE模块通过与SAA7113相连的VPO总线,采集标准的YUV4:2:2的Y分量(只采集Y分量目的是得到灰度图像),即其中的亮度信号,一行的图像含有720个亮度信息,亮度信息的位宽为8位。当FPGA_RAM1的图像行满时,发出行满信号ram1_full给DSP_INTERFACE模块,DSP_INTERFACE模块中将该信号转好为中断信号n_int_pulse以通知DSP调用EDMA获取该行的图像。同时进行内部RAM的切换,把下一行数据写入FPGA_RAM2中,保证一边DSP在读取一行图像数据,一边FPGA在写入下一行图像数据给另一个RAM ,以完成一次乒乓操作。

DSP在完成车牌图像的处理后,将车牌图像的识别结果通过EMIF写回到FPGA的DSP_INTERFACE模块内部的寄存器里,并通过UART模块获取这些寄存器的值,通过UART传到PC。

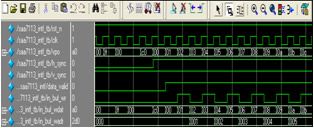

图6所示波形是图5内部框图中的其中一个SAA7113_INTERFACE模块在Modelsim上的仿真波形,从仿真波形中看出,与实际SAA7113输出波形是符合的,达到我们预期的结果。

图6 SAA7113_INTERFACE仿真波形

3、结论

本文所设计的基于DSP和FPGA的嵌入式车牌识别系统,具有速度快、稳定性高、体积小、功耗低等特点,为车牌识别算法提供一个较好的验证平台,如图7所示。经过验证,该车牌识别系统能够实现实时的图像采集、传输、识别。从时间上来考虑,在DSP内部单对一幅车牌图像完成处理(定位、归一化、特征提取与编码)只需不足400ms的时间,速度上来说是非常快的;从识别率上来考虑,只要算法达到一定的要求,经过该车牌识别系统运算后,识别率也是能达到非常高的。总之,该系统在车牌识别方面有着一定的应用价值。

最后,作为一个可以实际使用的车牌识别系统,在以后的系统设计中,还需要增加用于网络通讯的部分、及一些更智能化的功能,如液晶显示、声音提示等等。总之,嵌入式车牌识别系统是当前智能交通应用领域的重要研究课题之一,拥有广阔的应用前景。 |

|