[导读] 安全高效的状态机设计对于任何使用FPGA的工程师而言都是一项重要技能。选择Moore状态机、Mealy状态机还是混合机取决于整个系统的需求。无论选择哪种类型的状态机,充分掌握实现方案所需的工具和技巧,将确保您实现最佳解决方案。本文主要介绍如何在FPGA中实现状态机

关键词:状态机通信协议控制器FPGA

FPGA常常用于执行基于序列和控制的行动,比如实现一个简单的通信协议。对于设计人员来说,满足这些行动和序列要求的最佳方法则是使用状态机。状态机是在数量有限的状态之间进行转换的逻辑结构。一个状态机在某个特定的时间点只处于一种状态。但在一系列触发器的触发下,将在不同状态间进行转换。

理论上讲,状态机可以分为Moore状态机和Mealy状态机两大类。它们之间的差异仅在于如何生成状态机的输出。Moore状态机的输出仅为当前状态的函数。典型的例子就是计数器。而Mealy状态机的输出是当前状态和输入的函数。典型的例子就是Richards控制器。

定义状态机

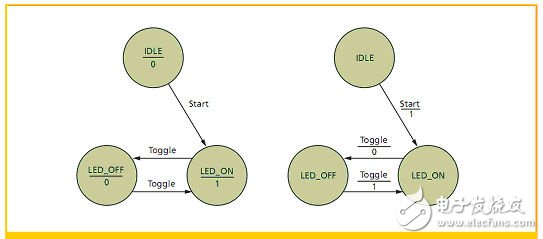

当需要定义一个状态机时,首先要绘制一张状态图。状态图可用来显示状态、状态间的转换和状态机的输出。图1显示了Moore状态机的状态图(左)和Mealy状态机的状态图(右)。

图1 用于开/关LED的Moore状态机(左)和Mealy状态机(右)的状态图。

如果您要在物理组件中实现这些状态图(工程师在FPGA问世之前就是这么做的),首先就得生成当前状态和后续状态表,然后生成实现状态机所需的逻辑。不过由于我们将使用FPGA来实现设计,因此我们可以直接从状态转换图开始工作。

算法状态图

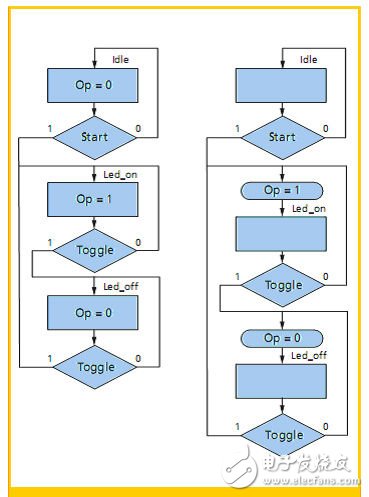

虽然有许多状态机是使用图1所示的状态图方法进行设计的,但另外还有一种描述状态机行为的方法,这就是算法状态图法。ASM图(图2)在外观上更加接近软件工程流程图。它由三个基本部分构成:

1.状态框。它与状态名称有关,并包含Moore状态输出列表。

2.决策框。如果检验某条件为真,则进行下一状态的判断。

3.条件输出框。让状态机根据当前状态和输入描述Mealy输出。

一些工程师认为,如果使用VHDL等硬件描述语言,则采用ASM格式进行描述的状态机更易于映射到实现方案中。

图2,用于图1所示的状态机(Moore状态机(左),Mealy状态机(右))的算法状态图。Moore和Mealy:应该选择哪个?

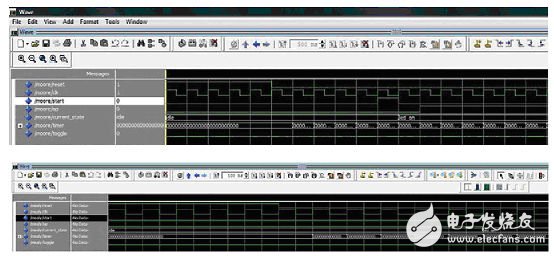

实现Moore状态机还是Mealy状态机,取决于状态机需要实现的功能,以及特定的反应次数要求。两种状态机之间的最大差别在于状态机如何对输入做出反应。在输入和设置的适当输出之间,Moore状态机一般有一个时钟周期的延迟。这就意味着 Moore状态机无法对输入变化立即做出反应,这点在图3中可以清楚地看到。而Mealy状态机则能够立即对输入做出反应,这通常意味着:实现相同的函数,Mealy状态机比Moore状态机需要更少的状态。Mealy状态机的不足之处就是在与另一个状态机进行通信时,如果输出出乎意料地严重依赖于其它事件的序列或时序,就可能会发生紊乱情况。

图3,截屏显示了Moore状态机(上)和Mealy状态机(下)输出的仿真结果。

当然,并非只能使用单纯的Moore状态机或Mealy状态机,也可以将这两种状态机混合使用,从而更有效地实现所需的函数。比如说,用于接收RS232串行数据的状态机就可以是混合机。

实现状态机

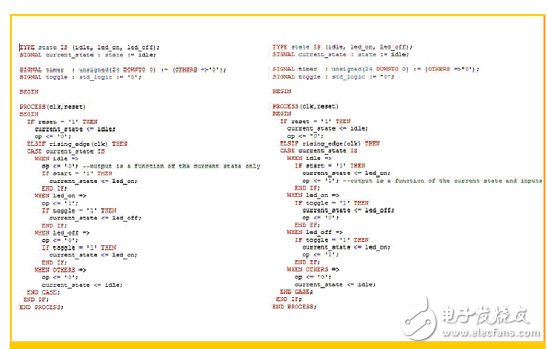

使用VHDL这样的高级语言,可以轻松地直接从状态图实现状态机。VHDL支持多种枚举类型,方便您定义实际的状态名称。举例如下:

TYPE state IS (idle, led_on, led_off) ;

上面的类型定义对应的是图1中所示的状态图,即用于在按下按钮时切换发光二极管开/关的状态机。

实现状态机有许多种方法,可分为两类基本方法。第一类基本方法就是一次性将所有内容集成到单个进程中。第二类基本方法是双进程法,将组合逻辑和顺序逻辑分开。

一般来说,大多数工程师都倾向于实现单进程状态机。与传统上讲授的双进程法相比,这种方法具有以下优势:

●可以避免组合过程中信号覆盖不完全造成的闭锁风险。

●状态机的输出与时钟保持同步。

●通常比双进程实现方案更容易调试。

无论您决定采用哪一种方法来实现状态机,都需要使用CASE语句来评估下一状态的判定和任何输出,如图4所示。该图并行比较了使用单进程法的Moore状态机(左)和Mealy状态机(右)。

图4,使用VHDL语言的Moore状态机(左)和Mealy状态机。 |