我们的手都曾有过静电放电(ESD)的体验,即使只是从地毯上走过然后触摸某些金属部件也会在瞬间释放积累起来的静电。我们许多人都曾抱怨在实验室中使用导电毯、ESD静电腕带和其它要求来满足工业ESD标准。我们中也有不少人曾经因为粗心大意使用未受保护的电路而损毁昂贵的电子元件。

对某些人来说ESD是一种挑战,因为需要在处理和组装未受保护的电子元件时不能造成任何损坏。这是一种电路设计挑战,因为需要保证系统承受住ESD的冲击,之后仍能正常工作,更好的情况是经过ESD事件后不发生用户可觉察的故障。

与人们的常识相反,设计人员完全可以让系统在经过ESD事件后不发生故障并仍能继续运行。将这个目标谨记在心,下面让我们更好地理解ESD冲击时到底发生了什么,然后介绍如何设计正确的系统架构来应对ESD。

简单模型

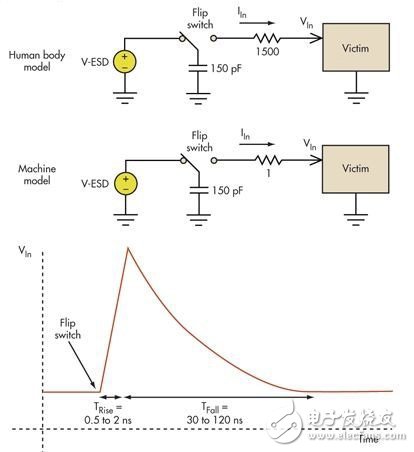

将一个电容充电到高电压(一般是2kV至8kV),然后通过闭合开关将电荷释放进准备承受ESD冲击的“受损”器件(图1)。电荷的极性可以是正也可以是负,因此必须同时处理好正负ESD两种情况。

图1:板级ESD通常涉及机器模型(MM)和人体模型(HBM)。

破坏受损电路的高瞬态电压一般具有几个纳秒的上升时间和大约100纳秒的放电时间受损电路不同,对正负冲击的敏感性可能也有很大的不同,因此你需要同时处理好正负冲击。人体模型(HMB)和机器模型(MM)这两种最常见模型之间的区别主要在于串联电阻。人体模型的导电性没有金属那么好。

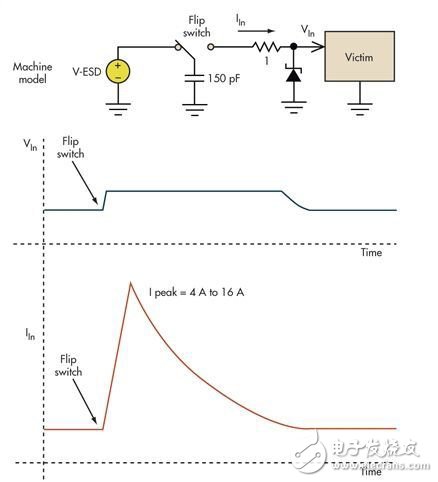

防止过压损坏的最佳保护措施是用非线性电路进行限压或钳位(图2)。最常用的是专门的二极管,当它们在前向偏置或处于齐纳击穿区时具有很低的阻抗。引入限压器可以快速引起某些别的事件,因为通过电容放电会有大的浪涌电流经过限压器。

图2:基本的限压电路可以防止过压损坏

虽然消除了高瞬态电压,但代之以几个安培的浪涌电流可能会导致系统中出现其它问题。具体取决于随后路径的总阻抗,浪涌电流可以达到几个安培。在为芯片设计I/O单元时,经常看到4A至16A的浪涌电流进入器件。处理如此巨大的瞬态浪涌电流已经成为ESD设计中的大问题。限制电压还算比较容易,但形成的电流可能使系统中其它地方的电路和地发生逆转。

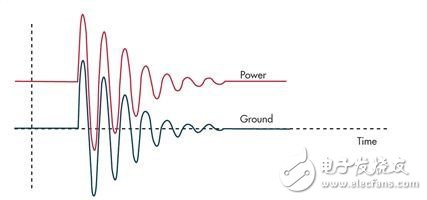

被限压器强制导入地的电流将在系统的那个节点中产生感应性振铃现象(图3)。电源通常沿着地线传播,并且是电源去耦电容的函数,因此系统核心仍能正常工作。不过连到电路板上的控制线可能出现混乱,因为它们是相对板外的地而建立的。结果可能在某个位置发生ESD事件,并致使电路板上的某个输入端看起来出现故障。

图3:通过限压器将大的浪涌电流注入到地将引起PCB地的反弹,并表现为连接电感的一个函数堡垒的作用

利用板级ESD,你可以尝试建立一个堡垒,并在“护城河”上建立多个受控的接入点。连接到“城墙”之外的部分可以被广义地分成几个类别:协议受控的数据、低带宽检测和控制线以及高速接口。前两个比较容易处理,第三个具有一定程度的挑战性。让这三部分免遭ESD破坏有几种不同的方法。

不管最终产品是什么样,某种形式的保护性外壳将成为设备的一部分。隔离外壳内的电路是需要仔细考虑的第一道防线。在理想情况下,连接电路板地的金属外壳通常能起使用,但现代产品经常采用非导电性的塑料或其它现代材料。

电路设计人员通常没法控制建造城墙的材料,但对保护堡垒负有不可推卸的责任。在设计外壳时需要注意,到达机箱外部任何部分的ESD都会有无数路径进入内部电路。

建立一个PCB能够自我防止ESD冲击的堡垒可以从低阻抗的接地方法开始。建立一个地基和正常的电源完整性可以让印刷电路板(PCB)保持整个板上的信号完整性,即使是受到巨大的地浪涌电流冲击的时候。

|