利用DSP48E1的pattern detection功能实现数据匹配

|

- UID

- 1023229

- 来自

- 中国

|

利用DSP48E1的pattern detection功能实现数据匹配

对于DSP48E1硬核的功能和结构,尤其是预加器、乘法器和累加器(ALU)的使用很多人都比较清楚,但对于它的另一个强大的功能pattern detection,很多人不是很了解,这里,通过对一个具体的算法实现流程的描述,让大家熟悉这个功能。

算法需求如下:输入数据位宽为16bits,从这个数据流中匹配32’Hf6F62828,一旦匹配成功,给出匹配指示信号。

对于此算法的DSP48应用如下:

1. 首先,由于算法主要是判断输入的数据是否等于32位常数OxF6F62828, 然后给出判断结果指示信号。考虑到资源最优化,如果并行同时处理16路数据,需要消耗16个DSP48 slices,如果使用时分复用的方式,则每个clock cycle完成一个case数据的比较,输入数据采用移位寄存器,每个时钟周期移动1位,构成一种case数据,送入DSP48 slice 做Pattern detector比较,同时输出是否匹配的指示信号。16个clock cycle完成16种case的比较操作。

2. DSP48E1一次操作可以完成48bits数据的匹配运算,因此我们同时做32bits数据的pattern detector操作,输入两个16bits数据(32bits)后开始移位操作,构成32种case数据依次同常数OxF6F62828匹配,32个clock cycle完成匹配检测。

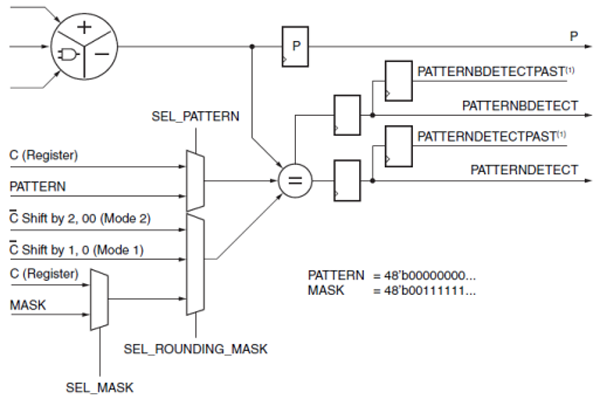

3. DSP48E1的pattern detector结构框图如下:

Figure 1: Pattern Detection logic 由于要匹配的pattern为常数,我们选择设置固定的OxF6F62828为图中的PATTERN值,使用MASK设置屏蔽掉高16位的比较,MASK设置为48’hFFFF00000000。输出PATTERNDETECT为高时,表示找到匹配的pattern。

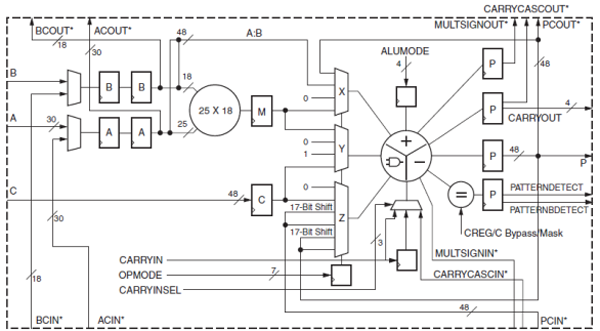

4. 上面Figure1中仅描述了Pattern的逻辑电路,DSP48E1的完整结构如下图2所示:

Pattern Detection的功能在ALU之后,所以,要将输入数据送入ALU后才能进行匹配操作。将32bits数据从C端口输入,高位扩展到48位(C要求48bits), ALU设置为C+0的加法功能,即将C的结果输出做比较。

为保证时序要求,打开C寄存器和PatternDetect寄存器,整个匹配链路的latency为2,这样经过32个clock cycle,所有32个case的匹配结果依次由PatternDetect输出为高可以确定是哪个case匹配。

5. 算法总结:

1)32bits移位数据从C端口输入到ALU单元,DSP48E1的OPmode设置为C+0功能。

2)在DSP48E1的属性中配置C打开1级寄存器,PatternDetect寄存器打开,整个计算通路2个clock cycle延迟。

3)在DSP48E1的属性配置中设置Pattern值为固定值0xF6F62828,并配置Pattern选择为固定寄存器值输入,设置MASK的值屏蔽高有效比特,低32bits用于匹配运算。

4)PatternDetect输出值为高时,对应的case即为找到的匹配数据。

|

|

|

|

|

|