by Luke Miller

亲爱的读者,我能问你们一个私人问题吗?这样才公平,你们知道这么多关于我的事情,所以我也需要了解一下你们…为什么你们仍然在手工编写FPGA设计?当然,你们不会再去手工编写一些接口,比如PCIe、SRIO、DDR、GbE、JESD204B、HMC等等…是这样吗?好的,那么为什么你们还在对世界上最好的、最了不起的Xilinx的FPGA的内核进行手工编码?是的,我确实说的是世界上最好的,在DSP、IO、SoC以及IP等方面都是最好的…那么你打算如何使用Xilinx Kintex-115器件中5520个DSP所提供的8TMACS计算能力呢?这是FPGA领域中带宽最大和速度最快的。

我们变得很安逸,不是吗?工程师们都不喜欢冒险和失去控制。我之前曾经说过这个,但我自2011年以来就一直都没有用C/C++手工编写过一个DSP的功能。让我们来看看Xilinx Virtex-II Pro器件中的232个DSP,我们都会为之喝彩,‘这就是我们想要的,不可能写出比它更好的了'!

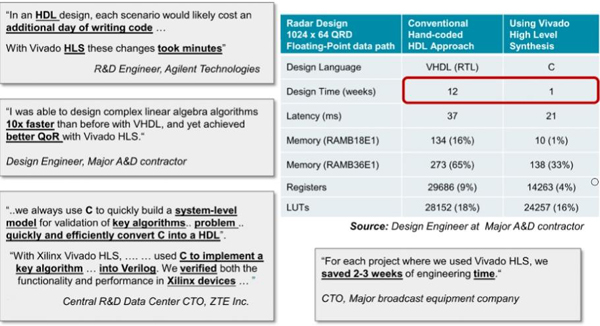

一个有着8块电路板,每块板上有3个Virtex-II Pro FPGA器件的VME,现在只需要几个UltraScale FPGA器件就能实现了,我想我们都同意这个说法。这是令人震惊的事,但是是谁在做固件设计呢?这就是问题所在。因为FPGA Blob持续地对周边的功能造成影响,所以如何去设计一个这样的系统并把它集成到FPGA中,对设计人员来说,这就是一个非常艰巨的任务。当我还是一个RADAR/EW工程师时,碰到的通常都是数学并行计算的问题。FIR滤波器、FFT算法、DFT算法、复数乘法、QR分解、CFAR等等等等…VHDL或者Verilog编码会让你按时地、符合预算地完成任务吗?我并不想破坏你的美梦但很可能做不到,而如果你的竞争对手正在使用Xilinx的Vivado HLS(高层次综合),那美梦就更是噩梦了。Vivado HLS可以处理定点或浮点数据类型,所以你需要去核定那个自适应波束成形器怎么实现吗?你可以很容易地在几个小时内设计出一个QR分解内核,可以处理实数和复数。从设计RADAR的角度看,这意味着你可以在一片Xilinx UltraScale FPGA中采用定点或者浮点设计出整个波束成形器、脉冲压缩器以及多普勒频率滤波器。这个想法可以应用到你所渴望的任何功能实现上。

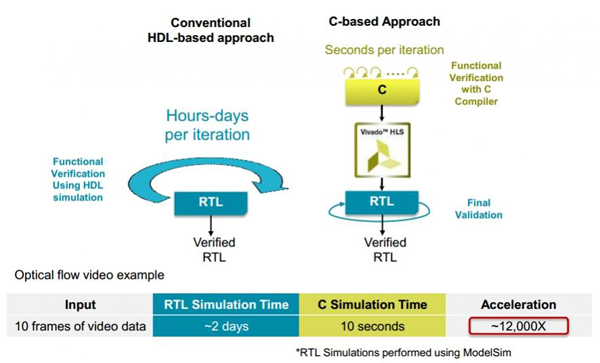

上面的结果都是真实的案例,他们都体验到了Xilinx Vivado HLS的强大,体会到HLS是战胜竞争对手的关键。因为仿真是采用编译好的C/C++可执行文件,而不是RTL仿真,因此整个设计时间大大缩短了。设计中的数学计算、延迟、器件使用情况和时钟频率都可以在几分钟内验证完毕。对RADAR系统中的一个多普勒频率滤波器卡进行RTL仿真,要花去几天的时间,然后要花几周时间去找出缺陷,修复设计。如果采用C/C++,仿真时间则是以秒来计算的。HLS设计也可以进行修改,并且非常方便。用在Xilinx FPGA的可编程逻辑上的代码可以很容易就编译到Zynq的ARM内核上,时间上的变化很象是以前从汇编语言移植到编译器那样。现在是时候开始使用Vivado HLS了,它是Xilinx FPGA设计人员工具箱中最有价值的工具。 原文链接:

https://www.semiwiki.com/forum/content/3472-secret-beating-your-fpga-com... |