在传统的大规模ASIC和SoC设计中,晶片的实体空间大致可分为用于新的定制逻辑、用于可再使用逻辑(第三方IP或传统的内部IP)以及用于嵌入式存储器三部份。

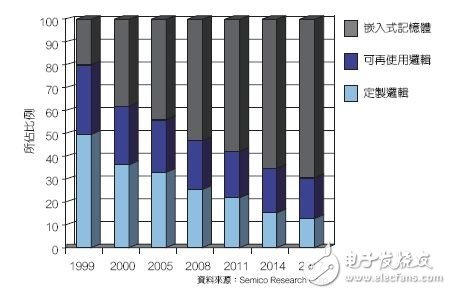

当各家厂商为晶片产品的市场差异化(用于802.11n的无线DSP+RF、蓝牙和其他新兴无线标准)持续开发专有的自定义模组,第三方IP(USB核心、乙太网路核心以及CPU/微控制器核心)占用的晶片空间几乎一成未变,嵌入式存储器所占比例却显着上升(参见图1)。

图1:目前的ASIC和SoC设计中,嵌入式存储器在可用晶片的总空间中所占比例逐渐升高

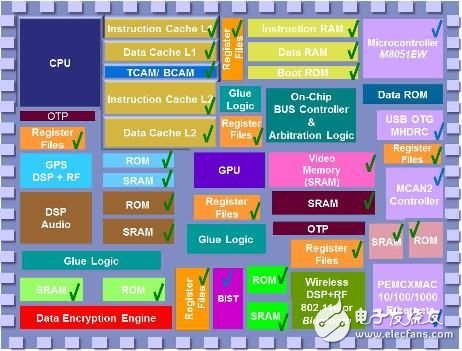

Semico Research 2013年发布的资料显示,大多数SoC和ASIC设计中,各式嵌入式存储器占用的晶片空间已超过50%。此外,许多大规模SoC嵌入式存储器的使用目的和主要性能也各不相同,如图2所示。

图2:多核心SoC的各种嵌入式存储器IP 由于可以根据设计目的,透过采用正确的SoC存储器类型来最佳化设计,因此,对于设计者来说,利用各种存储器IP具有非常重要的意义。设计者可透过恰当分配各种存储器IP所占比例,实现速度、功耗、空间(密度)以及非挥发性等各种性能参数的最佳化。

嵌入式存储器的主要设计标准

各种应用设计中,最佳存储器IP的确定主要基于以下5个驱动因素,如图3所示,包括功率、速度、可靠性/良率、密度,以及成本。

图3:确定存储器IP的主要因素

透过针对上述各种性能决定要素进行权衡,可得到最佳化解决方案。许多情况下,存储器编译器可根据输入存储器设计产生制程中的各种驱动因素,自动产生性能经最佳化的特定存储器IP。同样重要的是,存储器IP的支持性架构应适用可靠的验证方法,且产生的IP良率最高。最后,为了实现产量与品质最最佳化,存储器编译器还应直接产生GDSII,无需人工干预或调整。其他要素还包括良好的设计余量控制、对自动化测试图形向量产生和内建自测试(BIST)的支持。此外,最好具备通过BIST的单步执行进行硅片除错的功能。

功率 强大的编译器加上先进的电路设计,可大幅降低动态功耗(CV2f),并可透过利用多晶片组、先进的计时方法、偏置方法、电晶体Leff特徵控制以及多重供应电压(VT)最佳化等技术大幅地降低泄漏功率。设计者可整合运用这些存储器技术,透过电压和频率的调整以及多电源域的利用,得到最理想的结果。

速度 为了实现最佳化的存储器性能,充分利用先进设计技术至关重要。设计者可利用存储器编译器对速度(例如存取时间或循环时间)、空间、动态功耗以及静态功耗(泄漏功率)等因素进行权衡,得到所需要的最佳组合。在透过多种VT技术、多晶片组以及多种储存单元等的合成选用,改进存储器块的同时,辅以节能设计技术,同样可以获得较高速度。

可靠性与良率 电晶体体积和能耗的大幅下降,虽然使噪音容限明显减少,但也对极深次微米晶片的可靠性带来了影响。因此,为提高良率,改善执行的可靠性,需采用ECC和冗余技术。

由于现在SoC的位元数已十分庞大,因此,嵌入式存储器便成为决定SoC良率的最重要因素。在提高存储器良率方面,由于可减少量产时间,控制测试与修復成本,因此专有测试与修復资源具有重要作用。采用一次可程式储存技术制造的存储器IP,在晶片制造完成后,产生储存资讯失效时,其内建自修復功能便可对存储器阵列进行修復。理想情况下,为在生产测试过程中,快速进行修復编程,存储器编译器的修復功能必须与晶片测试工具紧密整合。

对于设计者来说极其重要的是,可根据需要选择由晶圆代工企业制造位单元,或者进行自我设计。当需要进行客制设计时,与理解客制设计且可为各制程节点提供硅片数据的嵌入式存储器供应商进行合作,具有极大的帮助作用。有了先进的设计技术,即使不需要额外的光罩和制程修正,亦可大幅地提高良率和可靠性。

密度 在存储器IP的选择上一个重要的考虑因素是,能否为各制程节点选择不同的存储器密度。先进的存储器编译器允许设计者在密度与速度之间进行权衡,比如,是选择高密度(HD)位单元还是选择高电流位单元。 |