老版本的ISE中曾经有stateCAD这个组件,可以很方便地进行FSM的设计;从ISE11开始,不再直接支持使用stateCAD进行设计了(也有绕过去的办法,见http://forums.xilinx.com/xlnx/board/crawl_message?board.id=OTHER&message... ),使得我们在设计FSM时需要手动编写HDL代码。那如何快速把HDL代码转换为图形化的FSM状态转移图呢?利用ISE和ModelSim配合就行了。

首先,在ISE中编写FSM的代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

module FSM(din,matched,clk);

input din,clk;

output reg matched;

reg[2:0] state;

parameter S0=8'd0,S1=8'd1,S2=8'd2,S3=8'd3,S4=8'd4;

always@(posedge clk) begin

case(state)

S0:begin

if (din == 1)

begin

state <= S1;

end

else

begin

state <= S0;

end

matched <= 0;

end

S1:begin

if (din == 0)

begin

state <= S2;

end

else

begin

state <= S0;

end

matched <= 0;

end

S2:begin

if (din == 1)

begin

state <= S3;

end

else

begin

state <= S0;

end

matched <= 0;

end

S3:begin

if (din == 1)

begin

state <= S4;

end

else

begin

state <= S2;

end

matched <= 0;

end

S4:begin

if (din == 0)

begin

state <= S0;

end

else

begin

state <= S1;

end

matched <= 1;

end

default:

begin

state <= S0;

matched <= 0;

end

endcase

end

endmodule

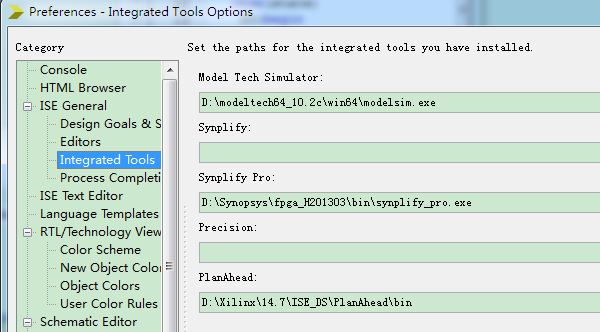

然后,配置ModelSim的路径,在ISE---Edit---Preference中更改:

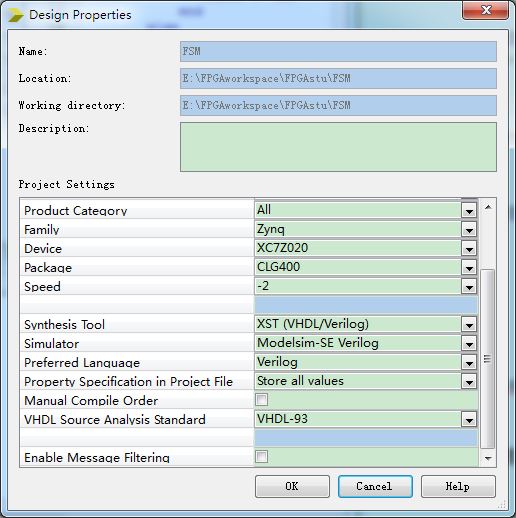

把仿真软件配置为ModelSim,方法是双击工程,或者右击工程选择工程属性:

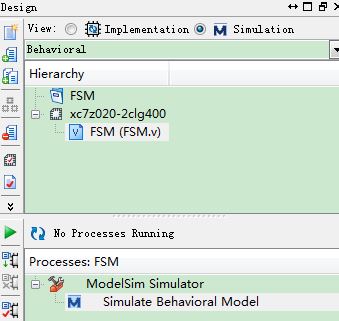

并切换为仿真视图:

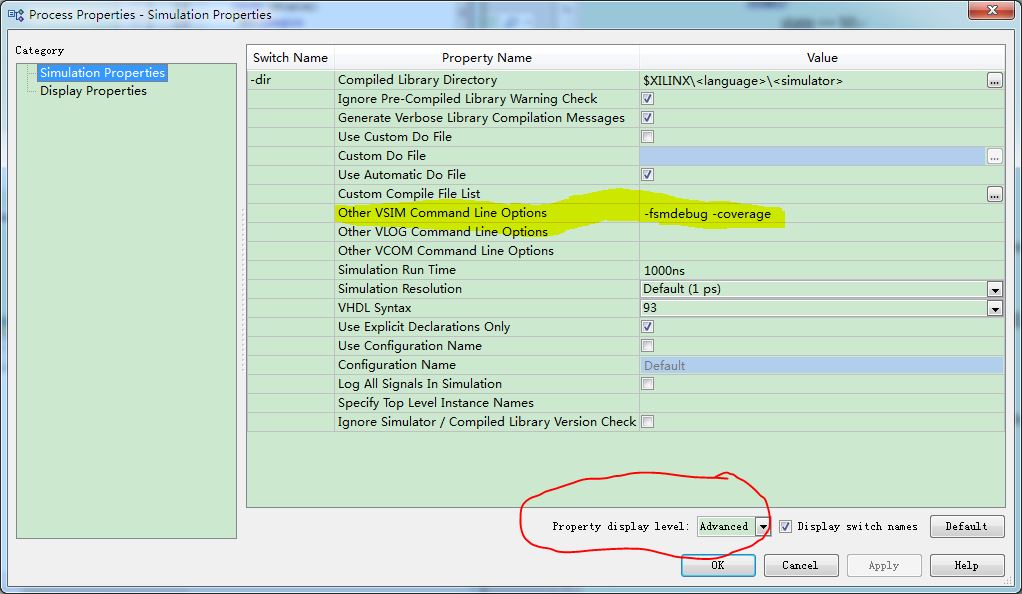

右键单击Simulate Behavioral Model,选择Process Properties。然后把Property display level改为Advanced,在Other VSIM Command Line Options下面,输入-fsmdebug –coverage这两个选项(务必输入,否则ModelSim无法产生FSM视图):

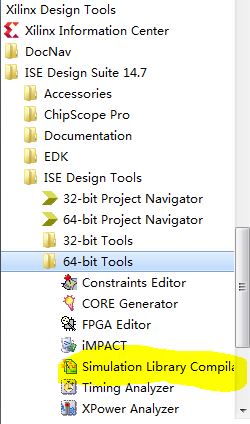

如果你还没有编译针对Xilinx的ModelSim仿真库的话,需要编译生成了(可参考http://xilinx.eetrend.com/blog/613)。可以使用Simulation Library Compilation Wizard:

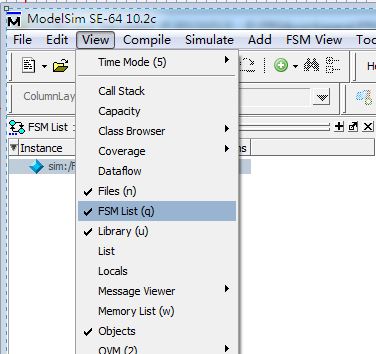

准备工作完成之后,在ISE中点击Simulate Behavioral Model,在ModelSim自动打开并编译完成之后,点击View—FSM List:

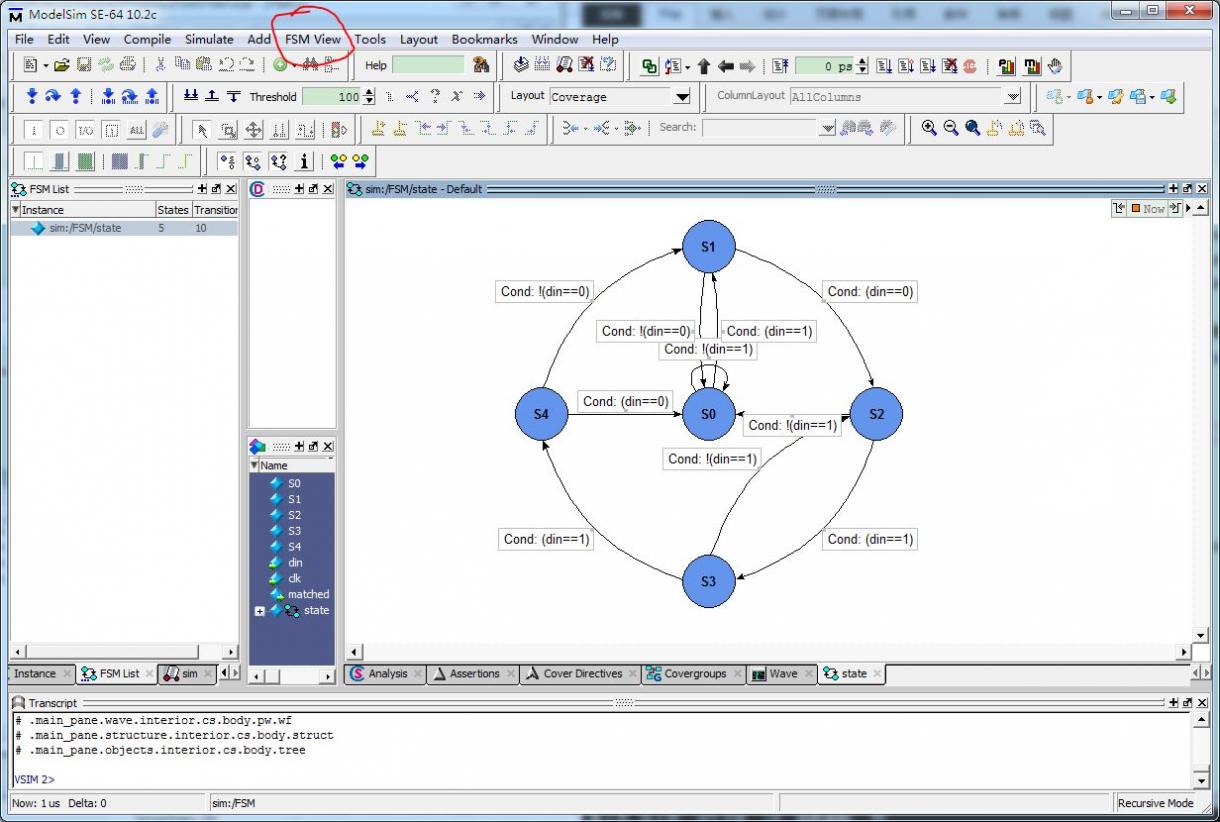

此时FSM视图已经自动生成了:

可以使用Ctrl+鼠标滚轮的方法对FSM图进行缩放。有意思的是ModelSim的缩放操作(滚轮向前是缩小)和一般Windows下的方向是相反的(滚轮向前是放大),和MAC OS里的自然手势一样,要习惯一下。 |