研究苹果的硬件总是一件很痛苦的事情,因为苹果在这方面从来都是极为封闭,绝少公开底层资料,因此绝大多数时候只能靠猜。

A7是苹果也是业内第一款64位架构的移动处理器,但是在iPhone 5S首发的时候,我们对它几乎一无所知。当时猜测它只是上代A6 Swift架构的简单改进版,解决了内存延迟等问题而已,但结果大错特错,严重低估了苹果。

iPad Air发布的时候,资料多了一些,首次知道其架构代号为Cyclone,还知道了架构方面的一些信息:

就目前看来,峰值发射宽度达到了六!也就是相当于A6、Krait的两倍,混合不同指令的时候更是能有三倍。

浮点、整数的共同发射局限也基本不存在了,可以并行发射最多四个整数加法、两个浮点加法。每个时钟周期还可以执行最多两个载入或者存储。

近日,AnandTech终于找到了苹果官方的LLVM文档,揭示和确认了不少细节,虽然仍旧比较模糊但在苹果的世界里已经不可能再深入下去了。

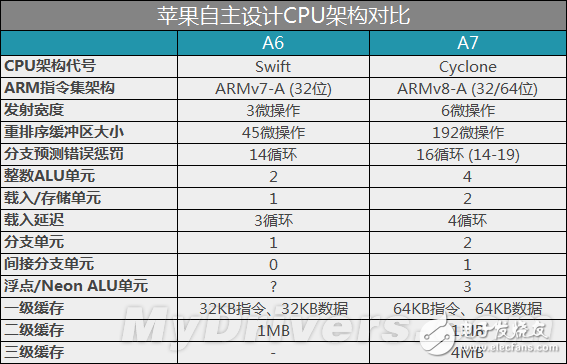

根据这份文档,A6、A7的架构规格对比如下:

之前猜测和推测的不少规格都是正确的。A7 Cyclone的确是一个很宽的架构,每个时钟周期最多可以同时解码、发射、执行、收回6个指令/微操作,A6 Swift则最多不超过3个。

A7的重排序缓冲达到了惊人的192,是上代的四倍多,同时巧合的是正好与Intel Haswell架构一样。分支预测错误惩罚也增加了,但幅度不大,而且又正好与Intel Sandy Bridge及其后的架构在同样范围内。

换句话说,苹果的架构已经在某些方面和Intel桌面产品架构处于同一级别了。

一级缓存容量的翻番可以理解,而在执行端,整数ALU单元、载入/存储单元、分支单元也都翻了一番,并首次加入了一个间接分支单元和至少一条浮点流水线,能够并行执行三个浮点操作,但注意第三条浮点/NEON流水线是用来做除法、开方的,乘法只能最多并行两个。

每个单元对应的缓冲尺寸也基本明晰,应该对应每个单元的微操作数,但在所有执行单元之前应该不会有统一调度器,而是每个端口前安置静态分区缓冲。 根据这些信息,A7 CPU架构简图是这个样子的(很可惜A6的还是没有足够数据无法直观对比):

六个解码器、九个执行单元端口,A7 CPU的确很“大”,比其他任何移动处理器都要大,已经完全超越了高通Krait、Intel Silvermont,足以媲美Intel Core酷睿架构。

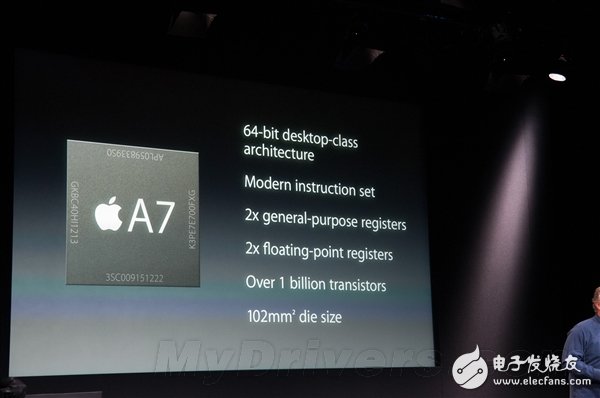

事实上,iPhone 5S发布的时候苹果就宣称A7是“桌面级别架构”(desktop-class architecture)——库克并没有夸张。

A7是苹果勇敢卖出的一大步,但正因为步子太大,应用还跟不上,至今没有一款能完全发挥其潜力,即便是苹果自己家的应用也做不到。A7 CPU就像一头沉睡的猛狮,等待唤醒怒吼。

另外,A7 CPU架构上很超前,但在内存上却很“吝啬”,iPhone 5S、iPad Air都只有区区1GB。尽管苹果可以做到只需少量内存就能把系统性能发挥到极致,但是1GB毕竟太少了,是不可能完全发挥A7 CPU潜力的。或许苹果意识到大家短期内做不到所以干脆就不浪费更多内存?

最后说一句,苹果起代号也不是即兴而为,看起来颇有深意:Swift的意思是快速敏捷,A6 CPU的确符合这个特点;Cyclone是旋风、飓风,A7 CPU确实很庞大。

接下来的问题是:苹果下一步会何去何从?A8又要冲击怎样的高度?

再做得更宽显然意义不大,但是性能改进仍有巨大的空间,尤其是提升频率和效率。A7的频率其实很低,iPhone 5S/iPad mini 1.3GHz,iPad 1.4GHz,相比于高通骁龙最高已达2.5GHz有点相形见绌。 |