基于Spartan-6的高速数据采集、处理和实时传输研究

|

- UID

- 863084

|

基于Spartan-6的高速数据采集、处理和实时传输研究

1.前言

随着信息技术的飞速发展,各种数据的实时采集和处理在现代工业控制和科学研究中已成为必不可少的部分,尤其在信号测量、图像处理、音频信号处理等一些高速、高精度的测量中需要对高性能的数据采集技术。这就为数据采集设备的设计提出了两个的要求:1)要求接口简单灵活且有较高的数据传输率; 2)由于数据量通常都较大,要求主机能够对数据做出快速响应,并进行实时分析、处理。

在基于软件无线电的接收机架构中,数字下变频(DDC)技术起着非常重要的作用,也是软件无线电的核心技术之一。数字下变频位于模数转换(ADC)之后,需要处理高速高容量的数据,因此难度较大,不容易实现。针对数字下变频中的这一实际问题以及数据采集设备的两个要求,本报告采用了一种基于FPGA与USB 2.0的数据采集与实时传输方案。

本文所研究的基于Spartan-6的高速数据采集、处理和实时传输系统,就是实现将宽带中频数字接收机输出的高速正交IQ数据传输给FPGA去实现软件无线电的后续信号处理算法。利用Cypress的EZ-USB FX2高速数据传输方案实现将基带数据或者经FPGA处理后输出的数据进行传输,并利用上位机软件进行上位机存储和显示。本文主要从系统的硬件设计和软件设计两个方面分别对高速数据采集模块(宽带中频数字下变频模块)、高速数据传输模块以及上位机软件三个方面进行详细介绍。

2.系统总体方案设计

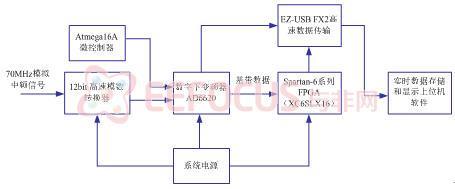

整个系统分成3个子模块,分别是:(1)高速数据采集模块(宽带中频数字下变频模块);(2)高速数据实时处理和传输模块;(3)上位机软件模块。整个系统框图如图1所示:

图1 系统整体原理框图

其中高速数据采集模块与EZ-USB高速数据处理和传输模块分别由对应的硬件电路和软件组成。上位机软件模块主要是利用Microsoft Visual2008软件利用MFC进行开发。系统整体硬件框图如图2所示:

图2 系统硬件组成框图

系统整体工作原理:首先高速数据采集模块对70MHz中频模拟信号进行模数转换,采样速率为60MHz(基于带通采样定理),然后利用Atmel公司的高性能微控制器Atmega16A作为控制单元以异步控制方式对专用数字下变频进行设置和编程,实现将中心为70MHz的数字中频信号搬移到数字基带,基带数据速率仍然为60MHz,因此需要对高速的数字基带信号进行抽取和滤波得到低速的数字基带信号,抽取倍数可通过编程设置,抽取倍数越大得到的数字基带信号速率就越小,低速的数据基带信号再传输给FPGA实现基带数据的码元恢复,得到原始信息。EZ-USB既可以对数字基带信号数据进行实时数据采集和传输也可以对FPGA输出的原始码元信息进行传输,最后通过USB2.0接口将这些数据传输到上位机进行数据实时存储和显示。

3.高速数据采集模块(宽带中频数字下变频模块)

传统的数据采集系统往往采用单片机或数字信号处理器(DSP)作为控制器,控制模/数转换器(ADC)、存储器和其他外围电路的工作。但由于单片机本身的指令周期以及处理速度的影响,其时钟频率较低,各种功能都要靠软件的运行来实现,软件运行时间在整个采样时间中占有很大的比例,效率较低,很难满足系统对数据采集系统实时性和同步性的要求。基于DSP的数据采集系统,虽然处理速度快,但成本较高,过于频繁的中断会使CPU的效率降低,响应速度变差。近年来,基于FPGA的数据采集方案逐渐成为一种具有特殊优势的一种方案,其中最主要的一个优点就是可以实现对数据的并行处理。另外还具有开发周期短,集成度高,功耗低,工作频率高,设计费用低,编程配置灵活等一系列优点。

本报告中采用的高速数据采集与实时传输方案,主要包括以下几个部分:1)高速数据采集以及数字下变频处理部分;(2).高速数据传输部分;(3).上位机数据采集控制部分。系统首先将外部真实世界的模拟信号进行数字化,然后将模数转换器的高速数字信号进行数据缓冲,然后将缓冲数据经过数字下变频处理后传输给FPGA,采用FPGA控制CY7C68013A实现高速数据实时传输与存储,并进行显示。 |

|

|

|

|

|