|

- UID

- 871057

- 性别

- 男

|

仿真对多模式RS编码算法性能进行了分析,并通过FPGA实现验证了算法在L-DACS1系统中应用的有效性,结果表明,多模式RS编码器可以实时地调整模式,高效稳定地进行差错控制,满足L-DACS1高速传输仍保持稳定的要求。

0 引言

为了解决地-空的数据传输业务增长而带来的高通信速度要求和高宽带要求问题,国际民航组织(ICAO)选定L波段航空数字通信系统(L-DACS)作为民航未来宽带航空数据链的传输方案。欧洲EUROCON-TROL 提出了未来航空通信系统(FAC),即L 波段数字航空通信系统类型1 和2(L-DACS1 和L-DACS2)。L-DACS1 是采用正交频分复用OFDM 技术的航空通信系统,它工作在960~1 024 MHz 的航空L 波段,被设计来满足未来20 年和更长时间的航空通信要求。

在L-DACS1 中,由于信道的噪声和畸变与多普勒频移的影响,会对传输的信息引起失真和信号判决错误,而且不同类型的数据需要采用不同的速率传输,因此需要使用多种模式的信道编码来降低误码率。RS编码是性能优良的纠错码,在线性分组码中它的纠错能力和编码效率是最高的。它不但可以纠正随机错误、突发错误以及两者的结合,而且还可以用来构造其他码类。因而RS编码是目前L-DACS1中重要的组成部分。

1 RS 编码器原理

RS(n,k,t)码通常用n、k 和t 三个参数表示。其中:

n 表示码字长度;k 表示信息段长度;t 表示可纠正错误符号个数。L-DACS1协议中采用RS(16,4,1)、RS(21,19,1)、RS(24,22,1)、RS(32,28,2)、 RS(43,39,2)、RS(49,45,2) 、RS(66,60,3) 和RS(74,66,3)八种模式。

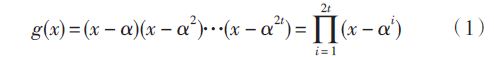

以RS(16,4,1)为例,RS(16,4,1)的生成多项式一般按式(1)进行选择:

首先计算商式h(x) 和余式r(x) n - k d(x) g(x) =h(x)g(x) + r(x) ,取余式r(x) 作为校验字,然后令c(x) = xn - k d(x) + r(x), 即将信息位放置于码字的前半部分,监督位放置于码字的后半部分,这样有式(2):

因此码字多项式c(x) 必可被生成多项式g(x) 整除。如果在接收方检测到余式不为0,则可判断接收到的码字有错误。RS编码器结构如图1所示。

其工作原理如下:

(1)寄存器R0 - R2t - 1 全部清零。开关接通A点,然后信息位分为两路送电路中,一路直接送入C(x) ,一路送入除法电路并进行移位。每一个时钟一个字节;(2)在k 个时钟结束的时候信息位全部输入,并完成除法功能。此时移位寄存器里保留了余式r(x) 的系数,这就是RS码的校验位;(3)在k+1 个时钟到来的时候,开关接通B 点。寄存器中的数据依次移出,送入信道。在经过2t 个时钟后数据全部移出,得到2t 个校验位。这2t 个校验位跟在原先的k 个信息位的后面,组成RS(n,k,t)码输出。这样就完成了RS码的编码;(4)寄存器R0 ~R2t - 1 全部清零,重复步骤(1)~(3),完成对下一组RS码的编码。 2 多模式RS 编码器的设计与实现

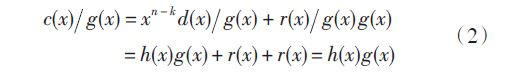

多模式RS 编码模块,根据MODE 信号对于可配置的RS 模块进行实时的配置。图2 为多模式RS 编码在L-DACS1 中硬件实现结构图,表1 为多模式RS 编码器模块端口说明。

根据协议规定,L-DACS1发射机使用归零卷积码,所以需要将RS编码器的输出数据末尾进行补零处理。因为卷积码的约束长度为6位,因此需要补6个零。

RS 编码后的数据放入缓存器中然后输出。根据MODE 信号对于计数器进行选择,计数器最大值时,将BUFFER 使能端置为低电平,同时激活ROM,顺序输出6个0值符号。然后计数器置为0,将BUFFER使能端拉至高电平。

3 多模式RS 编码器仿真

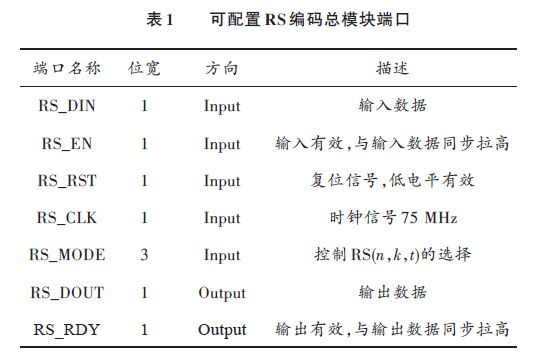

利用Verilog HDL 硬件描述语言对多模式RS 编码器进行仿真,对工程文件进行综合、布线和仿真,以RS(16,4,1)编码为例进行分析,其后仿真结果如图3所示。、

图3 中,MODE 是模式控制信号,可根据该信号来选择不同的RS编码模式。data_in为模块的输入数据,每次连续输入112 b数据;data_out为RS编码后输出数据,每次连续输出134 b;rdy 为数据输出有效标志位。

本次仿真RS(16,4,1)编码,模式信号MODE为000.仿真其他模式RS编码,改变MODE信号即可。

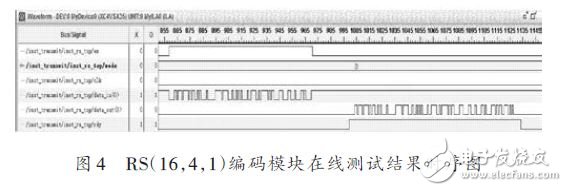

将仿真通过的工程文件使用ChipScope添加观察信号采样时钟、触发信号和待观察信号后重新综合、布局布线生成bit文件,下载到Xilinx公司的Virtex-5系列的XC5VLX110-F1153 型号的芯片后用ChipScope 进行在线测试,采用主时钟75 MHz,得到测试结果如图4所示。

图4中,en表示输入使能信号,data_in表示编码之前的数据,data_out表示RS编码后输出数据,rdy表示输出数据有效的信号,输入时钟频率为75 MHz,采样时钟频率为150 MHz.通过对比图3的仿真结果和图4的在线测试结果,可以验证在高速的时钟下设计的正确性。

4 结语

本文提出了一种基于L-DACS1系统中高速多模式RS 编码的设计方案。本方案先阐述了L-DACS1系统中多模式RS编码器的工作原理,利用FPGA设计实现了可以在高速多模式条件下正常工作的RS 编码器。同时用Verilog HDL 硬件描述语言对此设计进行了仿真验证,最后使用75 MHz的主时钟频率,在Xilinx 公司Virtex-5 系列XC5VLX110-F1153型号芯片下完成了硬件的调试,仿真及在线测试结果表明,达到了预期的设计要求,并用于实际项目中,以此证明该方案具有较强的实用性 |

|