FPGA 上的验证 - 一种基于USB2.0的视频图像处理芯片设计(3)

|

- UID

- 1029342

- 性别

- 男

|

FPGA 上的验证 - 一种基于USB2.0的视频图像处理芯片设计(3)

图5 所示的三张图片是仿真验证的过程中所涉及到图片,从图中可以看到Bayer 模块的设计达到了预期的目的。

图5(a) 用于生成Bayer 数据的原始图像。

图5(b) 由Bayer 数据未作坏点修正直接复原出的图像。

图5(c) 由做了坏点修正的Bayer 数据复原出的图像。

5.2 FPGA 上的验证

5.2.1 FPGA 上验证平台的搭建

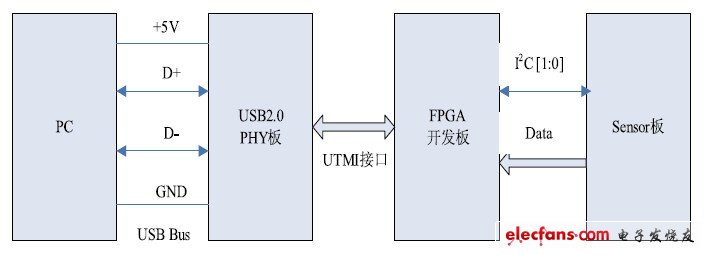

图6 所示为本设计的FPGA 验证平台示意图。

图6 FPGA 验证平台示意图。

PC 与一块USB2.0 PHY板通过USB2.0 总线连接,USB2.0 PHY 板与FPGA 开发板由标准UTMI 接口连接。Sensor 板主要是采用美光的MT9V112 sensor 板,I2C 接口主要是用于MCU 对Sensor 的控制,Data 总线包括数据总线和数据控制总线。而硬件MCU 模块、MCU Bus Interface 模块、USB2.0 SIE 模块、DMA 模块、PPU 模块和PU 模块均已综合生成FPGA 下载程序下载到FPGA 中。 |

|

|

|

|

|