|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

[导读] 随着摩尔定律的失效以及20nm、16nm和14nm工艺变得越来越昂贵,系统级芯片(SoC)的成本下降必须在更加成熟的工艺和既定的方法条件下进行设计创新才能实现。

关键词:SOC摩尔定律

随着摩尔定律的失效以及20nm、16nm和14nm工艺变得越来越昂贵,系统级芯片(SoC)的成本下降必须在更加成熟的工艺和既定的方法条件下进行设计创新才能实现。由于缩放到更小尺寸不会产生像过去那样促进半导体行业发展的相同的经济或技术利益,现在是时候考虑有什么别的可能来保持业务的增长和技术的创新了。

随着摩尔定律的失效以及20nm、16nm和14nm工艺变得越来越昂贵,系统级芯片(SoC)的成本下降必须在更加成熟的工艺和既定的方法条件下进行设计创新才能实现。公司期望能够通过率先推出普通产品、然后依靠使用更小工艺制造第二个更高性能版本来赢利的时代已经一去不复返了。

每一个设计小组都知道在以下方面实现质量改进的价值:更小的裸片尺寸;更高的带宽;更低的功耗;更高的生产率;灵活的服务质量。

然而,当下SoC设计的现实迫切要求我们尽快重新评估成熟的半导体工艺以实现更高的效率,进而实现更低的成本、更高的性能和更短的上市时间。由于缩放到更小尺寸不会产生像过去那样促进半导体行业发展的相同的经济或技术利益,现在是时候考虑有什么别的可能来保持业务的增长和技术的创新了。

总之,现在半导体行业需要更加关注优化芯片的初始设计,而不是寄希望于未来工艺节点缩小来满足成本、性能和功耗目标要求。

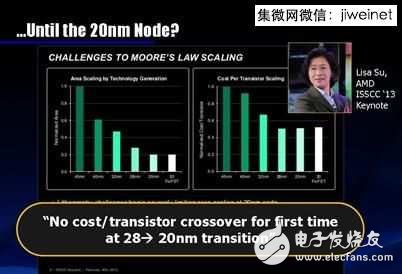

随着摩尔定律的失效,SoC公司应该寻找新的方法来优化设计工艺。下图展示了半导体行业面临的缩放挑战。

图1:半导体行业面临的缩放挑战。 更好的SoC设计 下面是一个更好的SoC设计以及一个更好的SoC设计工艺能够带来的一些定量好处。如果28nm工艺节点硅片面积的平均价格是每平方毫米大约10美分,那么裸片尺寸即使减小3至4平方毫米也能节省数百万美元。对于大批量产品来说,减小这个尺寸是可能的,目前正在为无工厂创新企业提供比竞争对手更有意义的经济优势。设计师还在尝试减少多达一半的走线和互连门。

芯片内更高带宽的连接可以提供更高的性能。1.6GHz以上的片上链路缩放可以改善工作在600MHz的子系统性能,并提高多媒体数据流的服务质量(QoS)。

更低的互连功耗最多可以将总的芯片功耗减少0.7mW,从而显著延长移动设备两次电池充电所需的时间间隔。虽然处理器和GPU功耗使互连功耗相形见绌,但它们只工作很短的一段时间。因此以互连功耗为代表的系统空闲功耗占系统功耗的主要部分。

生产率:在SoC设计领域中时间就是金钱。由100个人组成的软硬件小组每年的成本约为2400万美元,或每个月200万美元。如果某项设计工艺优化可以缩短30至35天交货,那么这个小组就可以节省200万美元以上的工程成本,并且还能比竞争对手更快上市。

上市时间:如果有方法能够将开发周期缩短二至三个月,那么大多数设计小组都会对这种方法特别感兴趣的。许多无工厂公司已经通过加快上市时间节省了400万至600万美元的成本。

初始设计:不再是每两年或每16个月生产一种SoC,现在可以每5至8个月提供某个主设计的派生品。大多数公司在设计周期后期都因为布线拥塞和布局布线问题而纠结于互连。然而,如果这些延时可以缩短甚至取消,那么无工厂公司就能提供更多的产品以服务多个市场。

如何快速改进SoC设计工艺

所有这些改进都发生在当下,从这些深厚市场和性能优势获益的小组开始放弃他们老的互连设计方法,转而采用网络芯片(NoC)互连IP。

对SoC设计的互连部分而言,一般有三种选择:继续内部努力;由分层总线和可配置交叉矩阵组成的互连IP;网络芯片(NoC)技术。

虽然SoC设计中越来越多的内容来自第三方IP提供商,但互连矩阵IP是仍处于过渡时期的一个领域。内部努力不可避免会半途而废,因为IP内容在不断增加,被分配了互连开发任务的设计小组无法跟上最新的变化和越来越大的复杂性。

由分层总线和可配置交叉矩阵组成的互连IP也在努力紧跟IP集成趋势,过去的40nm时代芯片通常有15个IP内核,而现在的28nm设计中会包含40个甚至更多个来自多家供应商的IP模块。

设计师应该评估能够驱动最高产品质量的互连技术。更低的产品成本和灵活的硬件架构应该享有同样高的优选等级。NoC IP最有资格用来同时提高产品质量和生产率。

如果SoC总体目标是要提高良率和质量,降低成本,那就好好考虑一下NoC互连IP可以提供而竞争性解决方案不能提供的优势:IP灵活性;工具自动化;建模输出;版图友好的建模输出;基于UVM方法的验证;自动测试平台生成;不同协议的支持;FPGA模拟映射;改进的市场响应能力。

世界上最复杂的一些SoC包括移动应用处理器和数字基带调制解调器,它们都集成了NoC技术,并作为SoC骨干互连矩阵使用。上述改进都是Arteris公司客户努力得到的真实数字。使用NoC互连技术带来的优化能力可以帮助这些公司提高芯片性能、降低芯片成本,从而提供明显的市场优势。

Arteris 公司从2006年开始就提供基于数据包的NoC互连IP解决方案了,在经过160多个初始设计、85个出带和50个电子系统中的产品化SoC之后,公司已经积累了相当丰富的经验。高效的NoC互连必须具有上述完整的性能和功能集,使SoC设计在质量、性能和生产率方面真正受益。

任何设计的互连部分都不应被视为普通商品:它是SoC的骨干,连接着SoC上的所有IP功能。当高效的NoC互连带给SoC的所有好处加在一起时,很显然性能和成本方面的收益可达数千万到数亿美元,具体取决于SoC的复杂性、SoC规格目标、项目数量和生产量。

|

|