|

- UID

- 1023230

|

1 引 言

小目标检测系统的任务是根据探测器获取的图像序列实时地把小目标从噪声中检测出来,它的实现是目标识别跟踪的前提和基础。小目标检测需要对探测到的图像进行实时处理,运算量巨大。另外,特殊的应用环境又对小目标检测系统在低功耗、轻小型化等方面提出了更高的要求。因此,完成小目标检测任务不仅需要寻求合理的小目标检测算法,在实现时还需要考虑处理性能和体积功耗。

2 DPA算法简介

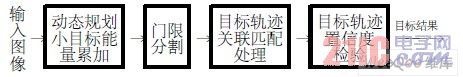

探测器与目标较远时,目标在红外图像上的成像面积很小,一般不超过探测器像元的大小,因此表现为小目标,而且图像信噪比很低。低信噪比条件下的小目标检测,首先要解决的是目标能量积累的问题。基于动态规划的能量累加算法(DPA算法)可以对小目标进行有效的能量积累。如图1所示,DPA算法主要包括三个部分: ①基于动态规划的小目标能量累加; ②门限分割; ③基于轨迹关联与置信度检验的目标轨迹处理,下面对这三部分进行简单介绍。

图1 小目标检测算法结构图

基于动态规划(DP)的能量累加算法是一种典型的先跟踪后检测算法。在多帧图像序列中首先估计目标的运动轨迹,沿轨迹进行目标能量积累,然后对能量积累后获得的图像进行检测判决。由于目标能量在不同帧之间是相关的,而噪声在不同帧之间是不相关的,因此沿目标轨迹上的能量积累将大于非目标轨迹上的能量积累,能量积累后的图像有效提高了信噪比,从而获得较好的检测性能。

经过动态规划能量累加后的图像为灰度累加和图像,此时目标点的能量远大于噪声,因此可以根据某一准则确定分割门限,剔除绝大部分噪声轨迹点,获得候选目标点集,进而完成目标检测。

经过目标能量累加和恒虚警门限分割后,得到候选目标集。从这些候选目标集中找到真实目标的轨迹,共需要四部分的工作:新轨迹的建立、轨迹关联匹配、目标轨迹状态预测、滑动轨迹置信度检验。

3 系统实现

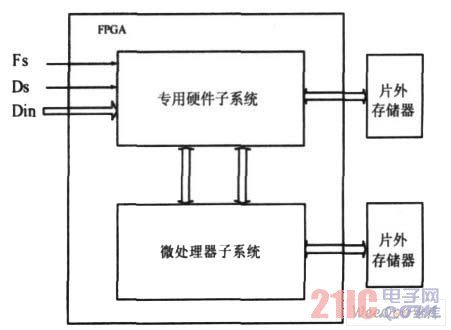

根据前面对小目标检测算法的特点分析,动态小目标能量累加算法操作简单,运算量大,处理时间要求严格,适合用硬件实现;而轨迹关联算法操作复杂,但处理的数据量小、时间相对宽裕,适合用软件来实现。在综合考虑了系统的体积、功耗、稳定性等因素后,最终选取了SOPC的实现方案,将整个系统集成于一块核心芯片———Virtex - 4 FPGA上。能量累加由构建于FPGA内部的专用硬件子系统来完成;轨迹关联部分则由Virtex - 4 FPGA内嵌的PowerPC405处理器来完成。

小目标检测系统总体结构如图2所示。

图2 小目标检测系统总体结构图

3. 1 专用硬件子系统设计

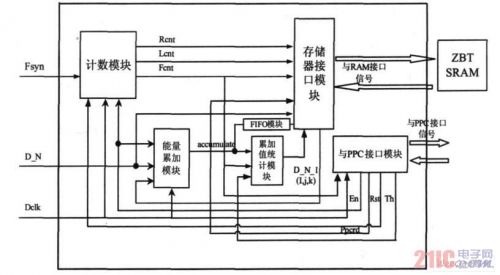

专用硬件子系统主要由6个模块组成:能量累加模块、累加值统计模块、存储器接口模块、PPC接口模块, F IFO模块、计数模块。如图3所示。

图3 专用硬件子系统结构框图

·能量累加模块:完成能量累加;·存储器接口模块:完成与外部存储器的接口工作,控制外部存储器读出与存储中间累加结果;·累加值统计模块:对能量累加后的中间累加值进行统计,计算灰度累加和以及灰度平方和,然后根据PowerPC微处理器传输的门限,对图像进行门限分割,对于超过门限的像素点,把该点的位置信息写到ZBT SRAM的相应地址空间;·PPC接口模块:完成FPGA 与PowerPC微处理器之间的接口工作。在系统运行之初,把PowerPC微处理器系统发出的控制命令信号以及PowerPC微处理器系统计算好的分割门限值写到专用硬件子系统相应的寄存器里,在图像分割好后,给PowerPC微处理器发中断,然后PowerPC会以中断响应的方式把ZBT SRAM中的候选点位置信息读到PowerPC微处理器系统的DDR SDRAM中;·FIFO模块:能量累加模块输出的灰度累加结果经过一个行FIFO 后写到ZBT SRAM里,更新第N - 1帧累加数据为第N帧累加数据;·计数模块:接收外部的帧同步信号( Fsyn) 、数据时钟(Dclk)信号,对其进行计数,从而产生控制所有其它模块的控制信号。

3. 2 微处理器子系统设计

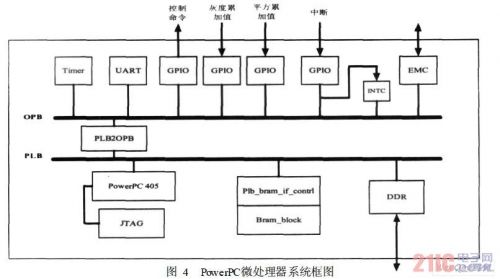

PowerPC微处理器子系统以PowerPC微处理器硬核为核心,通过处理器局部总线( PLB)与片内块RAM连接,进行高速数据传输;通过OPB总线与外围慢速设备进行交互,外设通过相应的外设接口IP控制器与总线互连。根据系统设计需求,需要用到的外设接口IP主要有: GPIO控制器(用于外部中断信号输入、控制命令输出以及单个数据的传输)、EMC接口控制器(访问外部ZBT SRAM)、DDR SDRAM控制器(控制DDR SDRAM)、UART控制器(与上位机通信,便于调试和产生按键输入中断控制系统功能)、Timer定时器/计数器(对轨迹关联及门限值求取的处理时间进行监控)、INTR中断控制器(多中断输入管理)等。系统组成如图4所示。

图4 PowerPC微处理器系统框图

4 PowerPC微处理器子系统调试及分析

为了验证开发的应用程序是否能实时实现轨迹关联,在应用程序中设计一个生成候选点的图像程序块, 生成好这些处理对象, 然后利用计时器( timer) ,监视处理完每一帧图像消耗的时间,同时把PowerPC微处理器子系统检测到的轨迹信息以及消耗的时间输出在超级终端,以检查PowerPC微处理器子系统的工作情况。

本次调试中,设计的每帧候选点图像中都只包含两个目标点,而且都按Vx = 1,Vy = 1的速率作匀速直线运动。图5给出一组轨迹关联测试结果。通过数据分析可知,系统处理一条轨迹长度超过15的轨迹平均耗时也不会超过0. 04ms。对于100帧/秒的输入图像数据,经过5帧一阶段的能量累加过后,得到的候选点图像帧频为20帧/秒。假设一帧候选点图像包含300个候选点,则可以设置轨迹关联最大预设轨迹数为1000,那么, 1000条轨迹的关联处理不会超过40ms,还在候选点图像帧周期之内。所以PowerPC完全能够实时完成轨迹关联任务。

图5 轨迹关联测试结果图

5 结 论

经调试验证, 本设计达到了预期效果。基于PowerPC的小目标检测系统能够实时实现小目标检测,而且硬件资源的余量以及处理器处理能力的潜力都为系统改进和升级提供了可能。 |

|