|

- UID

- 1023229

- 来自

- 中国

|

Excalibur是Altera公司的系列嵌入式处理器可编程逻辑解决方案,具有功率管理、系统可配置性和灵活性等特点。从物理结构方面看,单个Excalibur器件上包含了单端口RAM和双端口RAM、30万门的标准单元区域、嵌入式处理器IP内核和一百万门的APEX 20KE PLD,片上的晶体管总数达到了8千多万。其中嵌入式处理器内核IP包括基于ARM的嵌入式处理器、基于MIPS的嵌入式处理器或其它任何商用嵌入式处理器。

为了更好地把这些外部开发的处理器与APEX PLD结合起来,采用了一条嵌入式硅“带”(stripe)和复杂的多总线结构。这里的“带” 有别于正常的PLD区域,是指沿着Excalibur裸片的一条边定制的内嵌逻辑区域。将“带”和外围器件分隔开是有必要的,因为这两块区域的设计和布局方法完全不同。

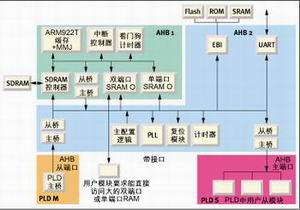

在功能结构上,Excalibur器件由4个AMBA AHB域组成,两个在带内,另外两个域则提供用于连接PLD部分的标准接口。为了能在单块可编程芯片上提供一个完整的系统,在内核结构中还集成了大量外围器件,比如EPXA10器件集成了ARM922T处理器、包括存储器管理功能的32位ARM9、8Kb I缓存、8Kb D缓存以及为便于系统调试的内嵌跟踪模块。

除了处理器外,带还包含:

1. 多个单端口SRAM和双端口SRAM。单端口SRAM容量可达256kB,双端口SRAM容量可达128kB。2. 一个SDRAM控制器。可支持单倍数码率(133MHz)和双倍码率(266MHz)的外接SDRAM,最大容量为512MB。3. 支持外接的FLASH、SRAM和存储器映射外围器件。4. 一个UART。5. 配置逻辑、可编程存储器映射和寄存器映射。6. 多个对不同域时钟去耦合的桥。

PLD IP的设计工程师在选取时钟时希望不会受到带的限制,因此在PLD AHB总线与带内部总线间加入“桥”。这样做的好处是终端用户能使处理器全速运行,而不必关心IP时钟与处理器时钟之间的时钟同步问题。由于所有这部分电路都置于带内部,因此用户可以避免设计用于时钟重新同步的逻辑电路。

不论是ARM处理器还是MIPS处理器都提供了很大程度的系统灵活性。在这种灵活性下,设计工程师可以开发出满足高端处理器性能要求的系统,该系统能满足复杂用户IP以及这种复杂IP可能带来的复杂时钟方案。由于这种灵活性主要面向Excalibur处理器的最终用户,因此对设计和校验提出了更高的要求。这种灵活性能实现产品的高质量,但同时增大了系统的开发难度,对系统校验也带来一定的难度,需要模拟所有从主控源到存储器区域的全部可能的信息情形,以及实现对读/写脉冲完整性的检查。

多总线结构

Excalibur ARM和MIPS系列处理器至少包含4条分立的AHB总线,还可以在PLD区域加入更多的AHB总线。系统设计为多总线,可以满足高性能、集成多个IP内核以及实现最终用户时钟的灵活性要求。通过减小高速总线的外围器件数量以及在两个总线之间建立一个连接桥,并将所有较慢外围器件连接到第二个AHB总线上,可以得到最快的时钟速度。

这些总线可以分成三层。最上二层完全包含在带内,而其它两条总线用于在系统的可编程部分集成用户IP。EPXA10是Excalibur系列产品中的第一个器件,在嵌入式ARM器件内的所有总线的宽度都为32位(参见图1)。

三层总线是目前能支持高速嵌入式处理器(200MHz)和关键外围器件(SDRAM控制器、单端口SRAM和双端口SRAM)以及AHB到AHB桥的唯一一种总线结构。低速AHB总线包含有地址映射逻辑、扩展总线、配置逻辑、UART、PLD主桥和PLD从桥。

在Excalibur设计中有三个方面的因素使校验工作变得更加困难,这些因素包括:多总线(multi-bus)结构、完全可配置的地址映射与时钟方案以及APEX PLD能实现的可编程设计空间。三层总线结构使得Excalibur“带”的设计与校验相当复杂,同时也增加了总线连接桥的复杂度。另外,系统中很多主要模块都具有二个独立的分离AHB接口,这些“双AHB”模块具有内部同步和仲裁逻辑,因此允许处理器与PLD直接访问主要的高性能存储器以及实现外围功能,如SDRAM控制器。

校验策略

由上述内容可知,Excalibur器件的校验策略必须是相当成熟的。由于设计上很复杂,校验人员的任务就是要确保器件的质量。同时校验环境要很容易地用于将来的换代产品中,并尽量方便工程师的使用。对于多数商业应用来说,开发时间很短,能减少开发风险也是很关键的因素。

对于许多开发人员来说,选择新的校验方案具有相当的风险。但Excalibur系列器件校验需要一种新的方法来满足先进技术方案的严格要求,以及易于复用和易于理解的要求。Excalibur校验环境是在Verisity公司的Specman Elite自动测试平台发生器基础上开发的,Specman Elite在校验环境的一些重要方面都实现了自动化。该校验环境能产生输入到器件的激励信号,并且这些输入信号是完全随机的,也可以是完全指定的,因此在设计中无需强迫系统进入某个确定状态就能达到特定边界条件。输入信号可以是校验前或空闲时生成,也可以在两种状态下生成。

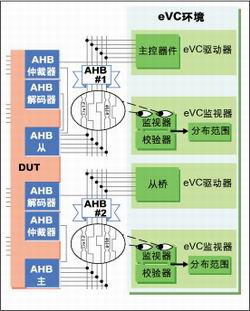

在上述校验环境中也用到了Verisity公司的AHB eVC(e校验组件),它是用Verisity公司的e校验语言编写的一段可复用的校验代码。AHB eVC是专门用于ARM处理器的AHB总线,是一种可复用的校验环境。

Specman Elite环境建立在AHB eVC基础上,并在multi-AHB的上层采用了宏语言。因此结合RTL与e主(e master)、e从(e slave)和总线仲裁可以创建一个虚拟的AHB环境。这样采用eVC就可以产生两种完整的AHB环境。从而使设计工程师能将来自每个环境中的主桥加入到Excalibur系统模块中,该系统模块由带、外部器件模块和伪PLD模块组成(见图2所示)。在ARM处理器的位置用一个AHB主桥,其它AHB主桥用在PLD桥接口。在两个主桥之间通过利用特定的初始化和协作机制,可以很容易地在完全“真实”的状态下校验存储区。通过每个主桥产生随机处理信息,能保证数百万的处理序列变换能准确对应每个多AHB模块。通过这种关系,这些复杂的传输信息序列能保证这些桥完全正常地工作。

因此,一个完整的Excalibur校验环境由AHB eVC、代码层以及大量的e宏(e macro)组成。其中在代码层可以利用多个eVC实例创建校验环境,并创建允许多个主桥运行的多种通信机制,而e宏实现用高级语言对有序和随机AHB传输信息排序。实际的校验环境大约由2,000行e宏组成,这比想象的要小得多。

宏语言

创建Excalibur校验环境的目标之一就是让不懂Specman的工程师也能轻松地利用该环境进行校验工作。通过在AHB eVC上用Specman Elite宏来分层置入“类汇编”语言代码,能方便工程师的理解。将宏语言分层置于e代码顶部的这种灵活性是该语言的独有特点,能确保所有工程师能在Specman Elite环境中轻松、有效地工作。

下面这个例子很好地说明了这种方法的作用:

//这是用于AHB1总线的发生器

//设置寄存器并产生同步事件

write_reg reg.MMAP_EBI1 value=0x4000_0881; write_reg reg.MMAP_EBI2 value=0x5000_0881;

write_reg reg.EBI_CR value=0x0008_0048;

//向SRAM发送脉冲以检查分离情况

write_read_burst 0x4000_000 check=TRU

size=WORD kind=INCR16;

//运行PLD主桥

write_reg 0x4000_0040 value=0xaaaa_5555

sync_event=TRUE sync_num=1;

multi_burst 0x4000_0000 to 0x4000_0700

num=5100;

};

//这是用于PLD主桥的发生器

extend PLD_M ahb_master {

write_reg 0x4000_0800 value=0x1234_5678

trigger=TRUE trigger_num=3

read_reg 0x4000_0800 exp=0x1234_5678

};

虽然绝大多数工程师对这段代码及其语法可能不太熟悉,但对这段代码的功能和结构并不难理解。这两段扩展块用来控制脉冲顺序,这些脉冲产生在校验结构框图中定义的两个输入点。每个块内的指令与汇编语言的符号相似,因此即使是不懂Specman Elite的工程师也能很容易地理解这段代码的功能。每个扩展块控制脉冲产生的次序,内含的通信机制使得一个主器件能在另外一个主器件跳出空闲状态前初始化寄存器映射。这种机制在测试过程中非常重要,因为二个主桥必须完全依据异步时钟的运行及其相互影响来保证某个特定的脉冲在另一个主桥的特定事件发生之时或之后产生。

事实上,大量的Excalibur系统级校验测试都是与上面类似的一些代码序列。这种宏语言与汇编语言的最大区别在于最后的 “multi_burst”指令上。这条简单的指令能向指定的存储器区域产生大量的AHB信号。这些信号的地址是在地址范围内的随机地址,并且大小与类型也是随机的,在同一地址上还包含有写信号以及随后的读信号,这样可以保证前一个信号写入的是同一数据。在多个时钟域以及任何随机访问存储区域中利用这种简单明了的机制能检查所有总线的完整性。

为了符合特殊情况要求,利用限制性机制能方便地将信号控制为一个脉冲宽度。另外,Excalibur芯片中存在大量的FIFO结构,因此能方便地创建FIFO全空或全满时的环境。

Specman Elite环境中,一个完整的校验环境由60多个用高级语言写成的测试组件组成。这些测试组件中最长的有600多行代码,整个测试平台大约有14,000行代码。相对于设计的复杂度来说这些测试代码相当少,用这么少的代码实现这么多的功能实在是无可比拟的。

如上所述,开发校验环境的目标之一是复用。AHB eVC就是按这种设想设计的,并且已经证明它能直接用于门级校验。事实上,这种校验环境已经在新一代Excalibur器件中得到了应用。

另外,Specman Elite很容易与用户开发的从闪存运行的ARM代码测试组件集成起来。这样就能实现对AHB2总线上仲裁的很真实的测试,因为在代码通过EBI从闪存执行的同时,可以通过PLD主接口输入处理信息。由于Excalibur设计和校验环境的通用性,使用这样的校验环境可以对任何的多AHB校验。Excalibur器件的用户也许正好想寻找与开发实际器件基本相同的环境,这也是今后的开发目标。 |

|