|

- UID

- 1023229

- 来自

- 中国

|

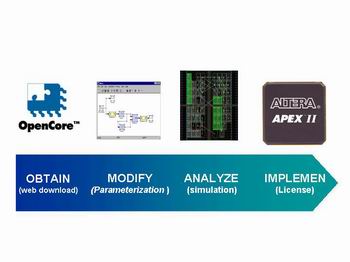

如何让设计师在购买IP之前对其进行充分评测,同时又保护内核及其源代码的知识产权,以防盗用,是PLD销售商、IP供应商和设计师共同面临的重要问题。本文中描述的技术就可以实现这些功能。它控制可用PLD编程文件的生成,同时允许IP评测者用特定PLD模拟和测试IP的所有其它性能,因而使评测者确定IP是否可以达到令人满意的效果,大大减小了设计师的风险,并缩短了设计周期,提高生产量。有一种称为“OpenCore”的技术,将IP集成在设计中,允许工程师试用第三方IP进行评测,而不必购买源代码。它采用了加密算法,可以保证评测者只有在获得IP销售商许可后,才能将IP集成在硬件中。使用这一技术,设计师可以在购买许可之前评测IP内核是否适合其系统,而不必承担任何风险。

因为IP许可的成本很高,IP评测者必须对IP内核进行无风险的试用编译,以验证开发者所宣称的功能性、密度和性能。开放式内核试用必须使用户得到足够的信息,以决定是否购买许可,同时又不可能在未付许可费的情况下将内核用于商业用途。

开放式内核假设整个IP评测中最重要的方面是顺利地将其集成在客户的设计流程中。这就需要在整个设计流程中处理IP,例如设计入口、逻辑合成和功能及时序模拟。该过程可能包含许多不同的设计工具。在整个评测过程中,既要保护IP销售商的专利权,又要保证评测者可以定制功能以满足特定设计的需要。

图1表示开放式内核的设计流程。

这一流程包括三个步骤:第一,合成器将HDL功能描述转换成逻辑原语网表。功能代码通常是RTL(寄存器转换级),大多用VHDL、Verilog或AHDL等标准语言编写。也支持基于纯示意图或混合示意图/HDL的设计入口。

第二步是将网表映射成可编程器件的物理原语,并生成完全布局布线后的设计,其中将包含实际半导体器件中的延迟信息。门级网表和布局布线后的网表均可以模拟,为设计师提高充分的功能和时序信息。

最后一步包括将布局布线网表集合在编程文件中。该文件包括各可编程逻辑元素的值以及编程信息位,例如校验和以及器件信息。编程文件包含设计的物理实现方法的二进制表示法。

参数化技术

为了避免定制,并尽量将可复用性最大化,内核应以高度参数化的形式提供。IP供应商有责任对每一内核进行参数化。大多数HDL支持参数化。例如,VHDL加法器的整个部分可以描述成:

ENTITY adderf

PORT (

dataa:IN STD_LOGIC_VECTOR (5 DOWNTO 0);

datab:IN STD_LOGIC_VECTOR (5 DOWNTO 0);

result:OUT STD_LOGIC_VECTOR (5 DOWNTO 0)

);

END adderf;

或者用通配代码参数化:

ENTITY adderp

GENERIC (

WIDTH : POSITIVE :=6; );

PORT (

Dataa IN STD_LOGIC_VECTOR (width-1 DOWNTO 0);

datab:IN STD_LOGIC_VECTOR (width-1 DOWNTO 0);

result:OUT STD_LOGIC_VECTOR (width-1 DOWNTO 0));

END adderp;

Entity Adderf的数据总线大小是固定的,而Adderp的数据总线大小可以任意配置。加密软件仍然可以保证对端口区以及通配区的访问。

为了方便地实现内核的参数化,很多EDA或PLD公司开发出了MegaWizard插件技术。Megafunction向导作为一种智能接口,可以引导用户高效、直观且错误较少的地对其相应的Megafunction进行规定和配置。理想情况下,它应根据用户在每一步所做的选择,引导用户进行所有的配置Megafunction的步骤。在大多数情况下,向导应由单个界面对象(对话框、多个控制或一个文本输入框)组成。但是建立向导的更加有用和直观的方法,是在一个向导页中集合一组相关的用户界面项目,允许用户在指引下从一页转至另一页。

可编程逻辑中用于试用IP的硬件功能

在很多情况下,IP用户要求进行硬件评测。当软件模拟难以实现,例如当软件模拟不能提供足够的故障范围,或者当软件模拟速度不足以进行整个测试,就需要进行硬件原理验证。

提供总线和接口设备(如PCI、USB或IEEE 1394)的IP供应商通常会建立一个基于PLD的演示模型和评测板,以补充其IP内核。对于PCI设备,硬件验证包含的增值服务包括:符合PCI电气要求,以及测试与系统中其它PCI商(如桥和主机)有关的功能交叠情况。使用可编程逻辑器件提高了原型板的灵活性。对同一块板,多个编程文件可以用于不同版本的内核。这些板可以用作演示硬件验证原理的工具。 |

|