FPGA电子电路设计图集锦TOP12 —电路图天天读(9)

|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

FPGA电子电路设计图集锦TOP12 —电路图天天读(9)

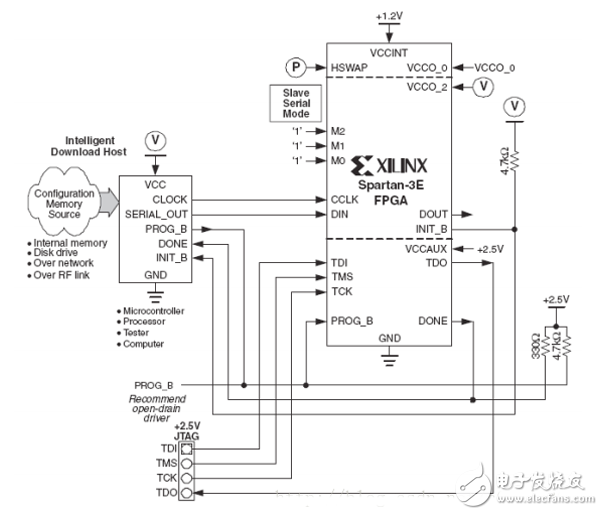

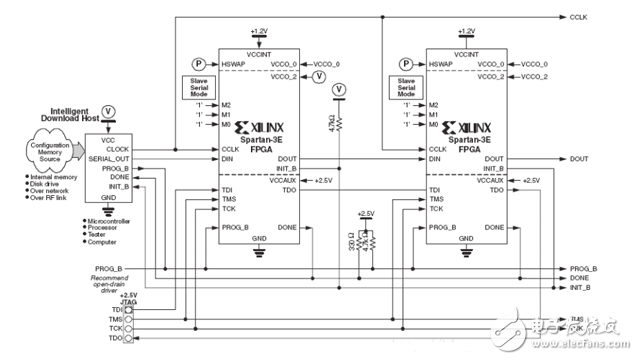

TOP9 重串模式的多片FPGA通信

DIN 输入管脚的串行配置数据需要在外部时钟CCLK 信号前有足够的建立时间。其中单片FPGA 芯片构成了完整的JTAG 链,仅用来测试芯片状态,以及支持 JTAG 在线调试模式,与从串配置模式没有关系。外部主机通过下拉 PROG_B启动配置并检测 INIT_B 电平,当 INIT_B 为高时,表明 FPGA 做好准备,开始接收数据。此时,主机开始提供数据和时钟信号直到 FPGA 配置完毕且 DONE 管脚为高,或者 INIT_B 变低表明发生配置错误才停止。整个过程需要比配置文件大小更多的时钟周期,这是由于部分时钟用于时序建立,特别当 FPGA 被配置为等待 DCM锁存其时钟输入。

以下是重串模式的多片FPGA通信:

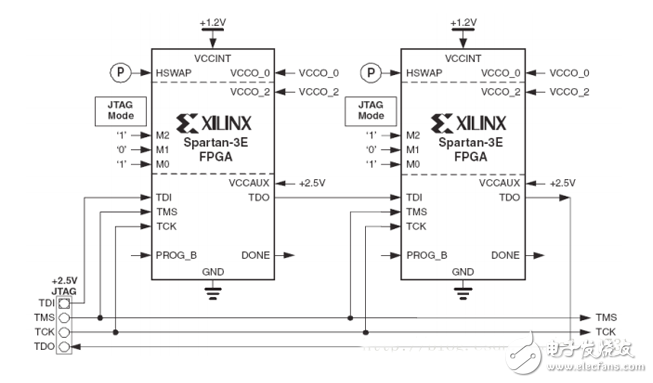

JTAG配置模式:

将模式配置管脚设置为 JTAG 模式,即 M[2:0]=3’b101时,FPGA 芯片上电后或者 PROG_B 管脚有低脉冲出现后,只能通过 JTAG 模式配置。JTAG 模式不需要额外的掉电非易失存储器,因此通过其配置的比特文件在 FPGA 断电后即丢失,每次上电后都需要重新配置。由于JTAG 模式已更改,配置效率高,是项目研发阶段必不可少的配置模式。

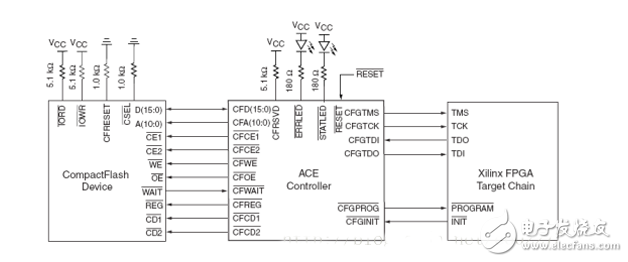

System ACE配置方案:

随着 FPGA 成为系统级解决方案的核心,大型、复杂设备常需要多片大规模的 FPGA。如果使用 PROM 进行配置,需要很大的 PCB 面积和高昂的成本,因此很多情况下都利用微处理由从模式配置 FPGA 芯片,但该配置方案容易出现总线竞争且延长了系统启动时间。为了解决大规模 FPGA 的配置问题,赛灵思公司推出了系统级的 System ACE(Advanced Configuration Environment) 解决方案。

System ACE 可在一个系统内,甚至在多个板上,对赛灵思的所有 FPGA 进行配置,使用 Flash 存储卡或微硬盘保存配置数据,通过 System ACE 控制器把数据配置到 FPGA 中。目前,System ACE 有 System ACE CF(Compact Flash)、System ACE SC(Soft Controller) 以 及 System ACE MPM(Muti-Package Module) 三 种。 |

|

|

|

|

|