|

- UID

- 1023230

|

要实现能够将所有重要功能集成在单一器件的设计理由很简单,因为这样就能将材料成本、部件库存及电路板面积减至最低。另外,相较于多芯片解决方案,单芯片方案的功耗也较低,同时也有助于提高对知识产权的保护。如果一项设计功能的精髓能够深植于单一芯片上,将会大大增加第三方取得这项设计的困难度。

单芯片系统对嵌入式系统设计师来说,往往会随着其面对的不同的系统设计而各有不同。例如,在庞大的娱乐或通信消费产品市场中,SoC意味着一颗具有数百万逻辑门的集成电路(IC),其中包含许多大型定制逻辑模块,并有将芯片的数字处理性能与外部世界连接的混合信号功能。在现实世界中,能够支持这样大规模的SoC开发的项目数量非常有限。

单芯片梦想

对大部分的设计团队来说,这样的SoC目标仍然是一个梦想。能够大量生产以支持一个完全定制化混合信号芯片开发的产品仍然是少数。绝大部分的产品都是采用专用标准产品(ASSP)或微控制器作为其解决方案的核心。在这样的情况下,想要找到一个能够完全符合项目需求的器件通常是一大难题。就定义来看,ASSP能够为某一特定应用领域的设计问题提供一种解决方案,但是这样的典型解决方案不可能完全符合真实世界中的项目需求。结果,通常是采用性能和参数超过需求的器件,或开发附加电路以弥补标准产品与实际需求之间的落差。此外,ASSP的灵活度不高,一旦选用了某颗IC,它的功能往往会限制产品后续的设计进展。

大部分的常用解决方案都不免会以微控制器(MCU)为基础。虽然其软件可编程性可提供不错的灵活度,但是很少有MCU能提供与典型嵌入式设计需求完全相符的功能。大部分这类的设计都会在MCU之外另加入不同形式的可编程逻辑(FPGA或CPLD),以增加硬件中的逻辑功能。尽管现今市场上有各种带有不同外设的MCU可供选用,但是绝大多数的嵌入式系统电路板上都没有提供各种作为信号调节和I/O连接用途的模拟器件。

混合信号FPGA

爱特过去一直在通过提供Fusion混合信号FPGA,为上述设计提供解决方案。Fusion混合信号FPGA在单一器件上结合了高密度可编程逻辑和可配置模拟电路功能,另外还包括大容量的闪存模块、完整的时钟生成、管理电路以及在FPGA逻辑中嵌入微控制器软核等设计选项。

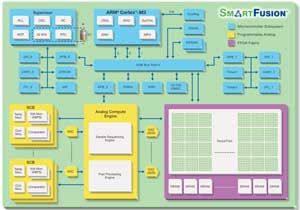

SmartFusion混合信号FPGA将高密度、基于闪存的FPGA、一个具完整外设组合的ARM Cortex -M3微控制器内核,以及高效可编程模拟功能全部都集成在一颗单芯片上。

图1 SmartFusion混合信号FPGA结构

ARM Cortex-M3处理器已不需要太多介绍。在SmartFusion芯片中,Cortex-M3处理器是个100MHz(125 DMIPS)器件,拥有最高容量为512KB的闪存和128KB的SRAM。在此系列FPGA中,处理器是一个硬核,这代表它是以最小面积来实现的,可带来多项好处。它的效能足以执行复杂算法,像精密电机控制、数个电机的多轴控制等。此外,在诸如系统管理等应用中,它能执行所有的电压监测、排序、风扇控制,以及相关的系统基本运作,同时还具备充裕的能力来执行更高级、用户应用级别的任务。

外设与接口

与在SmartFusion器件中以更小面积实现处理器硬核的方式相同,此器件也包含了常用外设的完整组合。

图2 SmartFusion系列器件具有丰富的外设及接口

SmartFusion器件提供一个10/100 Ethernet MAC(媒体存取控制器)和其他接口,诸如SPI、I2C以及UART。大量的数字(FPGA)I/O最快可执行350MHz,并支持LVDS、PCI和LVPECL等I/O接口标准。惯于采用微控制器进行设计的工程师会喜欢此器件所包含的其他特性和功能,例如,实时时钟、DMA控制器、外部存储控制器、定时器和看门狗(watchdog)功能。

在硅片上,除了ARM Cortex-M3内核,还有丰富的基于快闪的ProASIC 3 FPGA逻辑。此可编程逻辑可提供350MHz的系统效能;同时,SmartFusion系列器件最高可提供50万门的可编程逻辑和108KB的内建SRAM。基于快闪FPGA架构可完全免于由高能量辐射引发的固件错误(radiation-induced firm errors),此现象有时会影响基于SRAM的器件,同时也是许多嵌入式系统设计人员的主要考虑因素。由于FPGA的配置是设定在快闪单元(flash cell)中(ARM内核可从片上闪存执行),而整块芯片是上电即用,无须等待配置文件从ROM或EPROM加载的时间。此外,闪存也能允许用来进行现场升级,但是有时出于系统安全考虑,这种现场升级功能被取消。在编程结束之后,进一步存取配置存储器可被设置为永远停用。

在微控制器子系统内,有一个五层的ARM AHB总线矩阵架构,理论上共可提供片上每秒16GB/s的频宽。其中共有五个功能可供设定为总线主控(master):10/100 Ethernet MAC、DMA控制器和FPGA架构主控,另外两个来自Cortex-M3内核,而其他各种接口与存储模块则作为从属(slave)。

可编程模拟

SmartFusion器件的第三个重要元素是高电压双极模拟功能。为了正确获取来自应用程序的信号,SmartFusion器件最高可具备三个12位逐次逼近寄存器(SAR)模数转换器(ADC),其最高执行速度为600ksps。每个ADC都有相对的第一阶(first-order)1位sigma-delta DAC,能提供500ksps更新与12位有效分辨率。多个模拟功能都集中在信号调节模块(signal conditioning block,SCB)中,其中包含准确高电压和电流监控器、温度监控器和高速比较器。此高压监控器,也称为有源双极预分压器(active bipolar prescalers,ABPS),可提供-11.5V~+14V的电压监控能力。

此外,对系统管理或电源调节领域的设计人员来说,这也可作为绝佳的工具。器件中的电流监控器可放大从外部感测电阻测量到的电压降,而此感测电阻放置在应用的电流回路上,差分增益为50。温度监控器能把一个简单的PN结的电压降转换为温度读数。器件具备数量很多的片上比较器(在一50万门器件中最多有10个),而且速度非常快,传送时间仅为50ns。

自主(Autonomous)模拟信号处理

前面提到的模拟功能只是SmartFusion混合信号FPGA中模拟处理性能的一部分。而模拟运算引擎(ACE)是一个全新的概念,这是一个半自主的功能模块,无须ARM Cortex-M3处理器的介入,便能够执行完整的模拟前/后处理,包括信号采集的采样和排序。

由于ARM Cortex-M3内核就在ACE附近,初看起来在ACE模块中加入这样的功能似乎是多余的。然而,半自主的ACE可减少处理器内核的日常任务,例如,信号采集、处理、存储和输出等工作完全无须通过Cortex-M3处理器就能完成。设计人员能以这种方式配置器件,以使Cortex-M3处理器不受其他影响地执行实时处理任务。

在一个电源管理的设计工作中,监测每一电压轨是否偏离正常值以及警告等工作都由ACE来执行,它还有可应付更复杂的任务的能力,包括滤波和线性转换等。它所处理的可编程模拟模块包括ADC、DAC、和SCB。注意,此模拟模块拥有与微控制器子系统和FPGA架构的丰富连接组合。这些元素中的每一项,不管是单独或作为一组功能模块,其互连和工作参数都是可完全编程的。

设计灵活性更上一层楼

对于SmartFusion而言,器件和其相关的设计工具都已准备就绪,因此不管是具备何种背景的工程师,都能充满信心地执行一个完整的设计。

当利用SmartFusion器件进行设计时,一种基于图形化用户界面(GUI-based)拖放的操作方式(drag-and-drop-style)可提供对完整预定义IP功能库的立即存取。对C语言和RTL程序代码开发人员来说,此工具套件可扩展他们的专业领域,因此芯片的资源能充分被使用。此设计工具可提供协作环境,让传统的设计团队能针对SmartFusion的不同领域共同合作。

设计安全性

在现有的基于快闪FPGA系列器件中,爱特已对可编程逻辑提供了增强的设计安全性。ARM公司愿意将其处理器内核的软件版本授权给爱特公司,并在其FPGA中实现,就可以证明对于此设计安全性的信心。一旦编程到阵列之中,黑客将难以从硅片中读取此内核的IP。现在,微控制器内核与FPGA架构在相同的硅片上,此保护也延伸到系统软件以及FPGA配置码。ARM Cortex-M3是一个硬核,因此现已不需要这样的保护形式。

在单芯片环境中可提供固有的IP安全性,由于SmartFusion是一个快闪器件,因而不再需要从外部存储读取配置档案。在执行时,诸如FPGA到ARM内核总线的内部接口是看不到的,同时在它们上面的流量也无法监控。

此外,还有多种额外选项可供设计人员用来保护IP。最简单的方法是将存有FPGA配置的闪存以及Cortex-M3程序代码编程到“干净”的区域中,并设定一个“生效时切断保险丝”的条件,防止此闪存区域被读取或重新编程。此功能也称为FlashLock。从Actel Libero集成式设计环境(IDE)输出的资料,包含配置和运行时间(run-time)程序代码,也能用128位AES标准进行加密,以期在安全的制造环境之外也可以确保其IP得到保护。如果以匹配(matching)程序档案做好设定,一个内建的128位AES解密引擎可在最后的产品制造期间进行安全的系统内(in-system)编程。 |

|