|

- UID

- 1023230

|

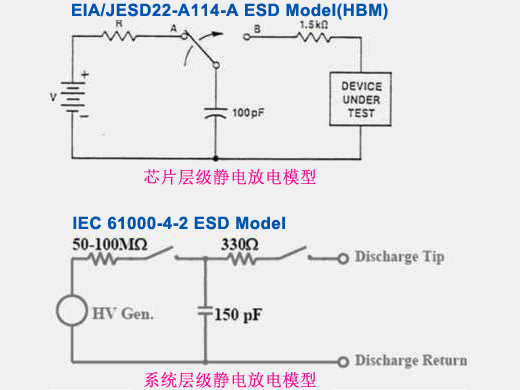

随着半导体制程技术的不断演进,以及集成电路大量的运用在电子产品中,静电放电已经成为影响电子产品良率的主要因素。美国最近公布因为静电放电而造 成的国家损失,一年就高达两百多亿美金,而光是电子产品部份就达到一百多亿美金之多。为了有效的防范静电放电所造成的损害,国际间众多的静电放电协会,分别针对不同的环境应用下制定了不同的静电测试规范。其中针对IC在生产、制造、测试及运输过程的静电放电规范,是以美国军方所制定的人体静电放电模型最具 代表性,又称之为芯片层级静电放电测试。而针对终端消费者所使用的电子产品,则以IEC 61000-4-2所制定的人体静电放电模型为测试主流,这就是一般认知的系统层级静电放电测试。

由于芯片层级和系统层级静电放电测试都是模拟人体静电放电,并且都是以kV为单位,所以常常造成大家的误解和困惑,我们在这里特别将这两种人体静电放电测试规格做一个比较整理:

模型电容电阻值规范不同:芯 片层级静电放电模型为对一100pF电容充电后透过一串联1.5kΩ电阻对待测物放电。而系统层级静电放电模型为对一150pF电容充电后透过一串联 330Ω电阻放电。由此可以看出在相同的静电电压下,系统层级静电放电模型将会具有较多的电荷容量和较大的放电电流,其放电能量约为芯片层级静电放电能量 的五倍之多,因此系统层级静电放电测试将会比芯片层级静电放电测试还要更严苛。而会如此规范的原因是,晶圆厂都会做工厂静电消除管理,所以IC在制造生产 的过程中受到静电的威胁较小。而电子产品用户所处的环境却是不受控制的,因此受到静电放电的威胁较大,这也是为何系统层级静电放电规范会制定的如此严格。

要求的静电放电电压等级不同:一般IC只会要求到芯片层级静电放电测试±2kV,而电子产品会要求到系统层级静电放电接触测试±8kV,空气放电±15kV。会这样规范的主要原因也是电子产品所处的环境是比IC所处的环境还要更严苛。

测试的失效准则不同:芯片层级静电放电测试是在IC针脚浮接的状态下做测试,一般造成的损害为硬件的损害。而系统层级静电放电测试是在电子产品上电运作的状态,除了可能造成硬件 的损害,也有可能造成当机或系统运作不稳定的情况。系统层级静电放电测试的失效问题是比芯片层级静电放电测试还要多更多。

以上就是系统层级 静电放电和芯片层级静电放电的基本差异,可以发现不论是在放电能量、静电电压和失效准则,系统层级都较芯片层级静电放电要求更严峻。随着电子产品要求高质 量的目标,系统层级静电放电的失效准则要求更有提高到Class A的趋势,这样更加深了系统静电放电设计工作人员的困难度。日前听闻国际上一些IC大厂为了加速产品上市量产的时间,有意将芯片层级静电放电要求电压下降 到±1kV,如此一来将更造成电子产品通过系统层级静电放电测试的困难度。因此了解系统层级和芯片层级静电放电规范的不同,和选用更高效能的瞬时抑制组 件,才能因应未来更严格的系统静电放电测试要求。 |

|