|

- UID

- 863084

|

高速数字电路互连时序模型与布线长度分析

高速电路设计领域,关于布线有一种几乎是公理的认识,即“等长”走线,认为走线只要等长就一定满足时序需求,就不会存在时序问题。本文对常用高速器件的互连时序建立模型,并给出一般性的时序分析公式。为体现具体问题具体分析的原则,避免将公式当成万能公式,文中给出了MII、RMII、RGMII和SPI的实例分析。实例分析中,结合使用公式分析和理论分析两种方法,以实例证明公式的局限性和两种方法的利弊。本文最后还基于这些实例分析,给出了SDRAM和DDR SDRAM等布线的一般性原则。

本文通过实例指明时序分析的关键在于:对具体时序理解透彻的基础上,具体问题具体分析,不能一味的套用公式,更不是通过走线的等长来解决时序问题。

1.典型高速器件互连时序模型

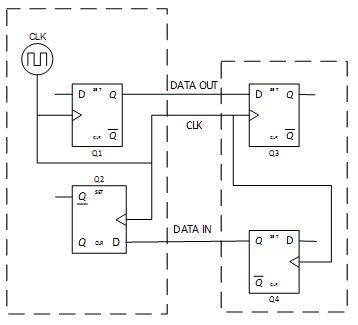

图1给出通用高速器件互连接口简化模型。图中,左侧虚线框表示通信器件双方的主控端。常见的实际情形有:SDRAM控制器、SPI主控制器等。经过适当的演化,基于本模型很容易得到I2C主控端、MII接口的TX组模型、RMII共享时钟模型以及DDR控制信号与地址信号的互连模型等。右侧虚线框表示通信中的被动端。本模型中,数据是双向的,但是时钟是单一方向。简单地说,就是时钟单一方向发送,数据双向传递。这个特点是本模型的适应场景。

图1简化的器件互连模型

图2是基于本模型的数据写时序关系图。图中,T0表示主控端内部时钟发生器CLK发出的时钟到达触发器Q1时钟输入端的延时;T1表示触发器Q1接受到时钟后到Q1输出端出现数据的延时;T2表示主控端内部时钟发生器CLK发出的时钟到主控端外部时钟输出引脚的延时;T3表示内部触发器Q1输出的数据到达主控端外部数据输出引脚的延时。通常,半导体制造商不会给出T0-T3这些参数,通常会给出一个用于反映这些参数最终等价效果的参数,即主控端外部数据引脚上出现数据时相对于外部时钟引脚出现时钟信号的延时,这里记为Tco.

图2数据写时序图

时序分析最关心的参数是信号到达接受端的最终建立时间和保持时间是否符合器件要求。这里将建立时间和保持时间分别记为Tsetup和Thold.Tflt-clk和Tflt-data分别表示时钟信号和数据信号的飞行时间,即他们在对应走线上的延时。Tjitter-clk和Tjitter-data分别代表时钟信号和数据信号上的抖动时间。 |

|