3.2 FPGA设计

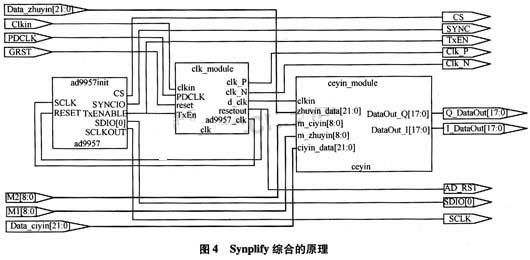

本设计中FPGA(现场可编程门阵列)采用XILINX公司生产的XC3S200,主要应用了VHDL可编程语言编写核心处理模块的硬件开发程序,其中包括时钟产生模块、侧音生成模块和初始化模块3个模块的设计。如图4所示。

时钟产生模块(clk_module)主要用来提供系统所需的统一工作时钟及AD9957所需要的差分时钟Clk_P和Clk_N,并为系统提供复位信号。

侧音生成模块(ceyin_module)中采用XILINX公司提供的DDS IP CORE直接产生所需主侧音和虚拟次侧音,通过计算控制字作为DDS的输入,即可得出相应频率的正弦信号输出,再与外围控制模块送进的各自的调相指数m1、m2经乘法器相乘后送加法器相加,最后经查找表输出两路正余弦信号作为AD9957的两路输入信号。

初始化模块(AD9957_init)用来产生AD9957的配置信号,如片选信号CS、串口数据写入SDIO信号等。使用Modelsim SE 6.0进行串口写数据的时序仿真如图5所示。

3.3 AD9957设计

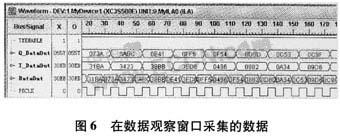

式(2)中侧音信号与载波信号进行正交调制后即可得到所需的侧音测距信号。在设计中使用AD9957的QDUC模式,由FPGA送出的I/Q两路信号与AD9957内部DDS生成的载波信号进行调相调制后输出,经带通滤波后即可得到所需的中频(70 MHz)USB信号。使用XILINX公司的ChipScope Pro 8.2i进行实时数据采集。ChipScope Pro是针对XILINX公司FPGA的在线片内信号分析工具,通过JTAG口在线、实时地读出FPGA内部信号。

数据观察窗口采集的数据如图6所示。

4 结束语

本文给出了一种基于FPGA和AD9957的侧音测距信号发生器设计,设计过程中充分利用了FPGA中特有的IP CORE来实现设计中所需的DDS、乘法器、加法器及查找表的功能,这样不仅简化了实现程序,而且节省了资源。同时通过外围控制模块的设计,实现了灵活的参数可控性能。

本文所设计的中频USB信号发生器已在某深空测距系统得以应用。 |