VGA驱动接口时序设计之5建立和保持时间计算 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

在我们的应用中,仿照官方的分析方法,我们也同样可以得到set output delay的计算公式。可以把实例的寄存器路径模型关键参数标注如图8.33所示。(特权同学,版权所有)

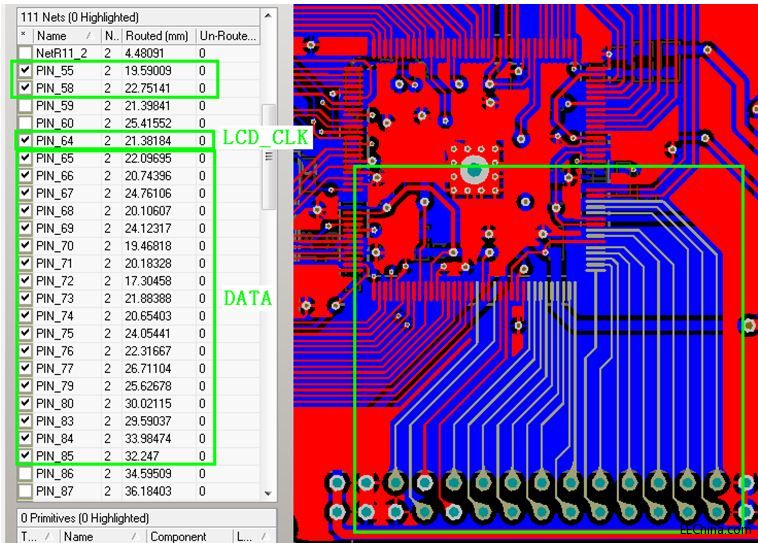

图8.33 reg2pin寄存器模型 而对于的output delay计算公式如下: output delay max = Tdpcb_max + Tsu +(0 - Tc2r_max) output delay min = Tdpcb_min – Th +(0 - Tc2r_min) 关于PCB的延时,我们可以看看SF-CY3核心板以及SF-VGA子板上的这部分时钟和数据走线。如图8.34所示,在SF-CY3核心板上,lcd_clk信号的走线约为21.4mm,而其他数据总线的延时在17.3mm~34.0mm。(特权同学,版权所有)

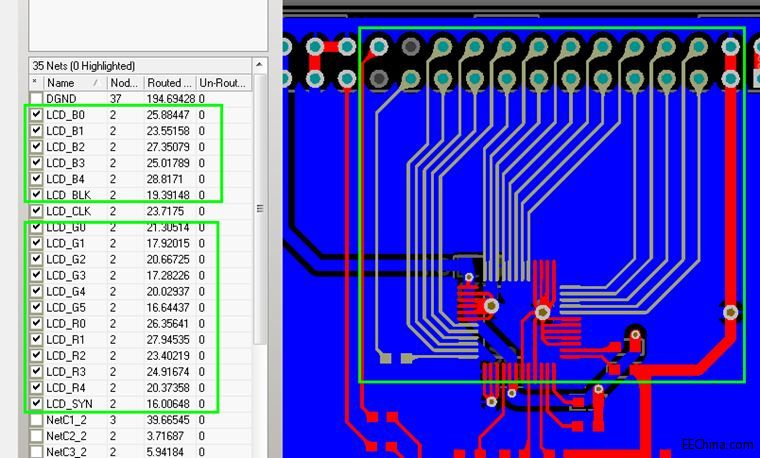

图8.34 SF-CY3板上各信号走线 在SF-VGA子板上,我们看到lcd_clk的走线约为23.7mm+5.0mm(匹配电阻的另一端,图中未显示数值)=28.7mm,而数据总线长度在16.0mm~28.9mm。(特权同学,版权所有)

图8.35 SF-VGA板上各信号走线 结合两个板子的走线延时,我们可以计算出时钟信号lcd_clk的走线总长约为50.3mm,数据总线的总长约为33.3mm~62.9mm。根据0.17ns/25.4mm的PCB走线延时进行换算可以得到,lcd_clk的走线延时约为0.34ns,而数据总线的延时约为0.22ns~0.42ns。(特权同学,版权所有) 把我们的参数套进去,我们先不计算时钟偏斜(包括PCB的走线延时)那部分的参数,可以得到: output max delay = 0.42ns + 0.2ns =0.62ns output min delay = 0.22ns – 1.5ns = -1.28ns |