基于Xilinx(赛灵思) CPLD的看门狗电路设计

|

- UID

- 852722

|

基于Xilinx(赛灵思) CPLD的看门狗电路设计

1 引言 :随着现代电子技术的发展,带有各种微处理的现代电子设备已广泛应用于国民生产的各行各业中。但随着设备功能越来越强大,程序结构越来越复杂,指令代码越来越长,加之现场工作环境的干扰,设备失控,程序“走飞”,各功能模块“死机”的概率也同样成倍地增加。对此,常见的解决方法是在电路设计时放置一片硬件看门狗(Watchdog)电路,其目的是在系统“走死”后能强制系统复位并返回初始化程序。随着CPLD器件被广泛应用于各种仪器、仪表设备的设计中,而且CPLD几乎可模拟任何一种逻辑电路,所以,现在在设计时已完全没有必要再放置一片独立的看门狗器件,而完全可以将硬件看门狗电路整合于CPLD 器件中,从而节省成本,降低系统的设计风险。下面具体介绍这种基于CPLD技术的看门狗电路的设计。 2 工作原理

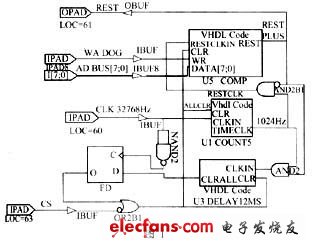

CPLD 是英文ComplexProgrammableLogicDevice的缩写,中文名称为复杂可编程逻辑器件,因其具有工作效率高、内部延时小、可预测延时等特点,而被广泛应用于计数器、逻辑电路、控制电路和复杂的状态机等功能的实现,而看门狗电路的核心就是一个计数定时电路,所以,利用CPLD特点将能很好地实现看门狗电路的功能。看门狗电路的原理框图如图1所示。它在结构上可分为分频电路、计数定时电路和复位电路三大部分,其工作方式是将一个 32768Hz的方波时钟输入分频电路,分频后的方波再输入到计数定时电路中进行计数,同时与已设置好的计数时间常数相比较,当CPU在指定的时间内没有通过改变CS端状态来将计数定时器清零,一旦计数值与预先设定的值相一致,计数定时电路将产生一个高电平给复位电路,复位电路将产生一个复位信号给CPU 的REST端。例如,对于MCS51系列单片机来说,将产生一个大于10ms的高电平以保证CPU可靠地复位。

复杂可编程逻辑器件 |

|

|

|

|

|