基于TMS320 DM642的多路视频处理系统设计

|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

基于TMS320 DM642的多路视频处理系统设计

近年来,DSP技术不断进步和发展,现有的高端通用DSP芯片,如TI公司的C6000系列,已具有最高可达5760MIPS的处理能力,广泛应用于雷达、移动通信基站等大运算量、高实时性的信号处理领域,同样也完全可以满足诸如视频处理等多媒体应用的要求。

但是随着视频监控市场的飞速扩大,目前市面上的一些视频监控系统缺点逐渐显现,包括成本高昂、路数少、实时性差以及画质不佳,且由于不同场合监控需求不一样使得用户对监控产品的灵活性和针对性提出了更高的要求。本设计采用TI公司的TMS320DM642多媒体处理芯片作为主控芯片,将成本控制在可行范围内,并且充分利用芯片内核的高速处理能力保证监控系统实时性,是一种兼顾成本及监控质量的好方法。

TMS320DM642(以下简称DM642)是TI公司于2002年推出的一款专门为数字媒体应用设计开发的32-bit定点DSP芯片,具备高性能的C64x数字信号处理器内核外且集成了丰富的外设资源,如可配置的音视频接口、以太网MAC控制器、JATG仿真器接口等。

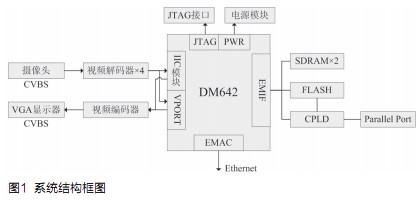

图1为整个系统的结构框图。以DM642为核心,主要包括视频模块、存储模块、通信模块以及其他外围电路部分。视频模块由四块编码器芯片和一块解码器芯片组成,采用切换方式以支持四路复合视频输入和一路视频输出显示;存储模块通过DM642的EMIF接口扩展片外存储器SDRAM和FLASH,并通过CPLD控制FLASH片内分页寄存器的读写;通信模块部分利用CPLD控制并口传输模式,实现时序逻辑以及数据传输,使整个系统作为从设备接受主设备控制以完成特定的图像处理运算等。

系统硬件架构

电源管理模块

DM642工作频率为600MHz,采取双电源供电方式:CPU内核电压+1.4V,电流793mA;外围I/O电压+3.3V,电流165mA。这两个独立电压在供电时需要严格按照顺序进行,保证内核电源先上电,最晚也应当与I/O电源同时上电,避免对芯片造成危害。

电源芯片,采用TI公司的高性能电源转换芯片TPS54310,它利用电路板上5V电源驱动两个线性稳压模块,经过两路电压转换生成所需的+1.4V及+3.3V电压,精度达1%。

上电过程中,在内核电压和I/O电源达到要求的电压之前需确保系统时钟处于复位状态,以避免产生不受控制的状态。因此采用TI公司的电源检测芯片TPS3823-33,它能够对系统使用最多的+3.3V电压进行监测,并且允许系统中各芯片在任意时刻通过复位来调整工作状态。

时钟电路

为了降低片外时钟频率,提高系统稳定性,在设计DSP系统时应尽量使用DSP片内锁相环(PLL)。在本设计中选用外部50MHz的时钟源,经过PLL进行12倍频后得到CPU所需的600MHz主频。在本设计中,采用1/4CPU时钟为ECLKIN提供150MHz的时钟,并通过ECLKOUT1引脚将时钟提供给SDRAM的CLK引脚。

整个系统中使用到的时钟频率还有视频编解码芯片的14.31818MHz时钟,它与DSP主时钟一样都采用外部有源晶体振荡器。

外部存储器

本系统主要用于视频图像处理,在处理过程中会产生海量数据,而DM642片内最多仅有256KB容量的RAM,所以必须扩展大容量的外部存储器才能够满足数据处理的需要。

本设计采用两片Hynix公司的HY57V283220T(4M×32bit)SDRAM芯片构成64bit外部RAM空间;采用一片AM29LV033C(4M×8bit)FLASH芯片构成外部ROM空间。将上述两片SDRAM芯片并联构成64-bit位宽、32MB大小的存储空间映射到配置为同步动态存储器接口、64bit位宽的CE0子空间。

视频通路模块

本设计中将DM642的3个视频端口VP0\VP1\VP2均设置为8-bitBT.656模式,其中VP0和VP1采用单通道方式,将通道A用于视频采集;VP2采用双通道方式,通道A和B均用于视频采集。因此,最多可以同时采集4路模拟视频信号。在BT.656视频捕获模式下,FIFO空间总共为2560KB且如下分配:1个1280Byte的FIFO专用于存储Y采样数据;2个640Byte的FIFO分别用于存储Cb和Cr数据。

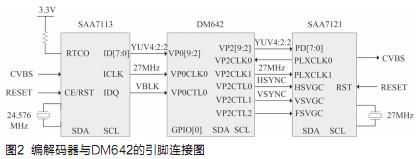

采用4片飞利浦公司的SAA7113解码芯片来实现4路模拟视频输入的转换。SAA7113支持6路复合视频信号CVBS或1路S端子(S-Video)输入,输出为带离散同步信号的8bit4:2:2YCbCr格式或者带内嵌同步信号的8bitBT.656格式的数字视频信号。

在视频回放部分,编码器选用1片飞利浦公司的SAA7121,其可将数字亮色信号(YUV)或数字RGB信号等数据转换成CVBS,S-VIDEO,RGB等模拟信号输出,支持PAL/NTSC制式,并且支持VGA及高清晰HDTV输出。

编解码器与DM642的引脚连接图如图2所示。

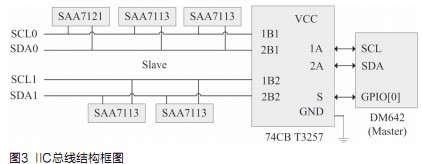

DM642中的IIC接口不支持高速模块[2],因此在本设计中所使用的IIC总线速率最高为400kbit/s。本设计中采用了TI的4bit 2选1切换器SN74CBT3257使DM642可以每次选择接收一组IIC数据。由于SAA7113只能配置两个不同的设备地址,一条I2C总线中不能同时连接4个SAA7113,因此须将IIC总线切分成IIC0和IIC1。具体连接方式见图3。

软件设计

设置DM642内部模块的配置参数,包括VPort视频端口参数配置,SDRAM及FLASH寄存器配置;IIC总线参数配置;编解码芯片内部寄存器配置等。

系统上电初始化,DM642通过内部软件模拟IIC总线时序,配置好SAA7113内部寄存器,设置其工作方式;之后DM642向CPLD发送采集指令,双方通过HOLD、HOLDA握手信号,实现总线控制交接,此时CPLD获得总线控制权,然后打开SAA7113的输出,对采集到的视频数据进行写控制;当一帧视频数据写入SDRAM帧缓存器后,CPLD关闭SAA7113视频输出,放弃总线控制权,并发送中断信号给DM642;DM642重新获得控制权后,对采集到的视频数据使用特定算法进行图像处理,并将处理后的视频数据缓存在SDRAM中,同时配置SAA7121内部寄存器,设置其工作方式,此时将SDRAM中缓存的图像数据送入SAA7121进行D/A转换,并经过并口送VGA显示器进行图像显示;DM642在图像处理完毕后即重新发出开始采集命令,进行下一帧数据的采集。

系统应用

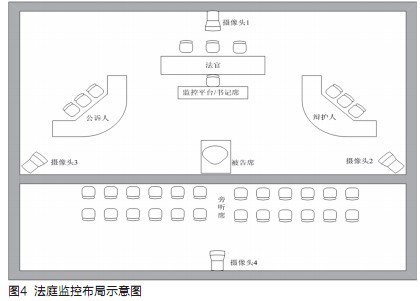

本设计在参考评估板的基础上,即成功裁减了冗余功能又保证了所需功能,大大降低了成本,节省了资源。本系统已应用在某法庭监控系统中(见图4)。其中摄像头1为被告席视频监控摄像头,摄像头2、3分别为公诉人及辩护人监控摄像头,摄像头4为法官席监控摄像头。数字监控平台可置于书记席处便于实时操作。整套系统建立在本视频处理系统设计之上,兼顾了成本与监控质量,已成功达到预期效果。

目前,业内主流还是基于CIF分辨率的视频监控,今后高分辨率D1的监控记录以及采用H.264技术的编码压缩产品的市场需求将逐渐增加,给算法优化及处理器性能提升提出了新的课题,这将是下一步关注的重点。

结语

整套系统充分利用了DM642的高速数据处理能力,其优点在于成本较低且具有较强的通用性和可扩展性。随着视频监控应用的快速发展,人们对图像质量以及实时处理的要求也会越来越高。基于DM642的嵌入式视频处理系统一定会越来越多地应用于多媒体数字信号处理领域,在工业应用及民用领域发挥越来越大的作用。 |

|

|

|

|

|