|

- UID

- 1029342

- 性别

- 男

|

FFTStreaming1/0数据流模块的工作流程:

在系统复位信号(reset)变为低电平后,数据源将 master_sink_dav置为高电平,对FFT函数来说,表明在输入端至少有256个复数据样点可以输入。作为回应,FFT函数将 master_sink_ena信号置高电平,表明其有能力接受这些输入信号。数据源加载第一个数据样点到FFT函数中,同时将master_source_sop置高电平,表示输入模块的开始。在下一个时钟周期, master_sink_sop复位,并以自然顺序加载后面的255个输入数据样点。在Streaming数据流结构中,FFT函数希望输入端口的输入数据连续可用,因此, master—_sink_ena一直保持高电平,除非系统复位,或由于master_sink_dav信号复位显示输入数据模块不完整,master_sink_sop信号置高电平失败,master_sink_ena信号才复位。如果要在一个输入模块的边界上停止模块数据流, master_sink_sop信号在前一个模块的最后数据样点输入以后就将保持低电平。FFT函数会复位master_sink_ena信号,并继续处理已经载入的数据模块。FFT函数中的流水线己经清除以后,master_sink_ena重新置为高电平,通过在下一个输入模块流的第一个输入数据样点上置位mastel_sink_sop信号来初始化下一个输入模块的读取。

当FFT己经完成了输入模块的变换,并且从设备源端将master_source_dav信号置高电平(表示数据从设备接收器可以接收输出数据模块)时,FFT将 master_source_ena信号置高电平,并且以自然顺序输出复数变换域数据模块。FFT函数在master—source_sop信号上输出一个高电平脉冲表示第一个输出样点。128个时钟周期后,master_source-eop信号被置为高电平,表示转换输出数据块结束。

三角滤波器组在前面已经介绍了,其重要计算公式是:

其中,每个三角滤波器的中心频率为T云(见表),这里引入T0和T24方便计算,则T0为0,T1为77,……,T23为7132,T24为8000。采样频率 16KHz,对于256个点的FFT变换,频率分辨率为62.5。用滤波器组的中心频率除以频率分辨率,计算出它对应于FFT频谱中的第几点,T0到T24对应的点为:

| 中心序号 | FFT中对应点 | 中心序号 | FFT中对应点 | | T0 | 1 | T13 | 33 | | T1 | 2 | T14 | 38 | | T2 | 3 | T15 | 43 | | T3 | 5 | T16 | 49 | | T4 | 6 | T17 | 56 | | T5 | 8 | T18 | 63 | | T6 | 10 | T19 | 72 | | T7 | 13 | T20 | 81 | | T8 | 15 | T21 | 91 | | T9 | 18 | T22 | 102 | | T10 | 21 | T23 | 115 | | T11 | 25 | T24 | 128 | | T12 | 29 |

|

|

根据上表,计算出 和 和 的值建立一张大小为128x23=2944的表,分别对应 的值建立一张大小为128x23=2944的表,分别对应

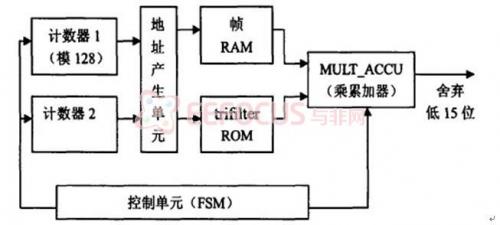

FFT频谱中的点。帧RAM中数据为16位正整数。三角滤波器组的值都在0-1之间,为方便计算将滤波器组数值定标为16位Q15,所有数字都扩大2“15=32768倍,并保存在ROM中。则三角滤波器的输出就变成:

其基本结构如下:

取对数

通过三角滤波器后的数值为16位正整数,去底数为10的对数lg(x),可以换成底数为2的对数,这样就变成了log2(x)的值,略有改动的是将两个表放进一个DPROM中,这样可以同时读出两个数,最后结果也不为31位的Q15,因为要乘以常数0.301,所以最后结果为47为Q30,第一位为符号位。

16位正整数最大为32767,而lg在(0,32767]上是单递增的,所以最大数为lg(32767)=4.515,为了保证一定的精度,结果取47中的34到19位,即结果为16为的Q11,1位符号位,5位整数,11位小数,这样的取法有利于接下来的DCT计算。

这一部分的实现是利用Verilog编程语言实现的。 |

|