吐血推荐,动态可重配置片上网络平台的系统实现,设计大赛获奖作品

|

- UID

- 863084

|

吐血推荐,动态可重配置片上网络平台的系统实现,设计大赛获奖作品

项目背景及可行性分析

项目名称: 动态可重配置片上网络平台 项目主要内容:通用的多处理器片上网络结构,以及通用网络结构设计方法;在动态可重配置技术的基础上,根据实际通信中的通信情况来进行任务分配和算法分解,确定片上网络路由方式和仲裁算法,以达到片上多处理器网络的任务均衡,尽量少的通信时延和通信量,尽量大的并行性,然后实现片上多处理器系统结构模型,建立基于FPGA的片上网络平台。

关键技术: 动态重配置、片上网络结构设计、片上网络路由仲裁算法

创新点:在研究片上多处理器互连技术的基础上,研究了片上多处理器网络技术,并提出大规模片上多处理器网络的设计方法,为具有超强计算能力的芯片设计的关键技术突破提供了预先研究。

随着多计算IP 复用设计和实时处理研究的深入,从2002年起,我们开始了收集与片上计算网络相关的资料,并对片上计算网络的设计方法论,实际应用与片上计算网络之间的映射方法、片上多处理器核的网络通信机制以及全局异步本地同步(GALS)系统等问题作了深入的研究,尤其是片上计算网络中IP或处理器之间通信技术的预先研究,也获得了国家自然科学基金的支持 [60575031,“复杂SoCs片上通信关键技术研究”]。重点突破通用片上网络的结构、通信协议、路由以及资源映射技术进行研究。2006年我课题组又成功申请了Agilent Technologies Foundation基金项目,“Multi-DSP Infrastructure for Measuring Device Based on NOC”。该项目要建立一个可用于通信密集测试任务的片上计算网络,这可以作为本项目的一个应用实例进行分析和验证。

项目实施方案

1.方案基本功能框图及描述

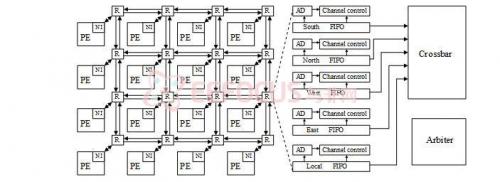

图一 设计的MESH结构网络框图

图一为一个带有处理单元的4×4 Mesh结构网络,每个交换节点连接着一个处理单元或IP核和四个相邻的交换节点,IP通过一个网络接口(NI)与交换节点相连。IP可以是一个处理器核、内存、专用计算电路、一个用户自定义模块或者是其他任何可以和网络接口相配的模块。交换节点与交换节点之间,交换节点与处理器资源之间是由一对输入和输出通道连接。通道由两组单向的点对点总线组成。

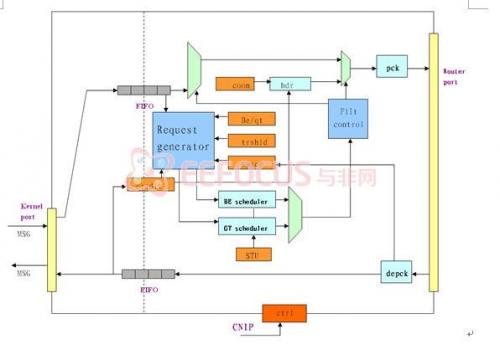

在NOC中,交换节点的设计是整个网络的关键,图二给出了一种带有虚通道的交换节点的内部结构框图。

图二 带有虚通道的交换节点

图三 动态配置管理单元

图三中的动态配置管理单元的主要功能是根据各个IP具体的数据流量,按照任务分配和算法分配策略对相应的路由节点的仲裁方式等进行动态配置。

图四 NI核心结构

NI模块主要完成IP与路由节点的连接,实现数据结构的转换。

2.需要的开发平台

(1) 实现本方案所需要的基本功能、接口:

平台上的FPGA含有ICAP,支持动态内部重配置;

平台上的FPGA时钟速率至少100MHz;

支持PowerPC;

平台上含DRAM、SRAM或FLASH存储器。

(2) 所需要的目标FPGA开发平台,简述为什么需要此平台

目标平台为Virtex II Pro开发平台。

原因如下:本项目属于大规模复杂片上网络设计,需要硬件处理平台具有较高的处理速度和丰富的逻辑资源,而Virtex-II Pro XC2VP30含有3万个Logic cells,因此能够胜任本设计;本项目需要该开发板中的ICAP协助重配置开发;另外板上FPGA内含有两个PowerPC硬核,便于测试时进行数据统计、结果分析。

需要的开发工具包括MATLAB、ModelSim、Xilinx ISE、EDK等。

3.方案实施过程中需要开发的模块

本方案中需要研制、开发的主要模块如下:

- 路由节点

- NI(Network Interface)接口

- 处理单元

- 重配置管理单元

4.系统最终要达成的性能指标

建立片上网络的MESH结构模型,通动态配置路由方式选择,以及仲裁模式选择,最终形成通用的多处理器片上网络结构平台。

需要的其它资源

1.设计输入输出功能子板

不需要

2.测试设备

包括直流稳压电源、万用表、示波器、逻辑分析仪、PC机等 |

|

|

|

|

|